# uSDCONF1A データシート

## ( for ALTERA ユーザ)

(uSDCONF1A5-001)

Rev 0.30 2014.02.17

Rev 0.20 2013.07.02

Rev 0.10 2013.06.21

悟空 株式会社

注)データシートとして ALTERA 用 Xilinx 用がありますが、モジュール自体は共通で差異はありません。

本データシートでは、ALTERA 用 FPGA に特化して、その使い方を説明しています。

## 改訂履歴

| 日時         | 担当者 | Rev  | 改訂内容概要                                                                                                                                                                                                                                                                                                                                                                         |

|------------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2013/06/21 | 大庭  | 0.10 | 初版(暫定)                                                                                                                                                                                                                                                                                                                                                                         |

| 2013.07.02 | 大庭  | 0.20 | P33 ⑥#P:C5 タイミング波形追加。<br>PS モード時の自動切替機能の記述修正、追加。<br>P43 9.4 最大 8 個接続のための記述追加。                                                                                                                                                                                                                                                                                                  |

| 2014.02.17 | 大庭  | 0.30 | P5 D1,D2 パラメータ記述追加。<br>P6 ③ゲートサイズ変更項目削除。<br>P26-28 D1,D2,P0 パラメータ変更に伴うタイムチャート差し替え。<br>P35 (i) #P : PM パラメータ追加。<br>#P:DR 削除、D2 に名称変更。<br>P36 (j) #P:D0 削除。<br>(k) #P : D1 記載事項変更。<br>(l) #P : D2 追加。以降の項番振り直し。<br>P41-42 8.4 D1,D2,P0 の設定設定について 更新。<br>P43 8.5.コマンドパラメータ デフォルト値修正。<br>P52 添付コネクタ型格誤記修正。<br>P53 13. uSDCONF2A=>uSDCONF1A 誤記修正。<br>14. 表 14.1 更新。<br>P54 ①制約事項追記。 |

|            |     |      |                                                                                                                                                                                                                                                                                                                                                                                |

|            |     |      |                                                                                                                                                                                                                                                                                                                                                                                |

|            |     |      |                                                                                                                                                                                                                                                                                                                                                                                |

|            |     |      |                                                                                                                                                                                                                                                                                                                                                                                |

|            |     |      |                                                                                                                                                                                                                                                                                                                                                                                |

|            |     |      |                                                                                                                                                                                                                                                                                                                                                                                |

|            |     |      |                                                                                                                                                                                                                                                                                                                                                                                |

## 目次

|                               |    |

|-------------------------------|----|

| 1. 機能・特徴                      | 5  |

| 1.1. uSDCONF1A の機能・特徴         | 5  |

| 1.2. uSDCONF1F からの修正点         | 6  |

| 2. 形状                         | 7  |

| 3. 電気特性                       | 8  |

| 3.1. 絶対定格                     | 8  |

| 3.2. 推奨動作範囲                   | 8  |

| 3.3. 消費電流                     | 8  |

| 3.4. 電源シーケンス                  | 8  |

| 3.5. リセットに関して                 | 8  |

| 4. Pin 機能表                    | 9  |

| 4.1. uSDCONF1A ピン機能表          | 9  |

| 4.2. XAREA 詳細                 | 10 |

| 5. 接続例                        | 11 |

| 5.1. uSDCONF1A 接続例            | 11 |

| 5.1.1. FPP/PS モード選択式          | 11 |

| 5.1.2. PS モード固定               | 13 |

| 5.2. uSDCONF1A Multi FPGA 接続例 | 15 |

| 5.3. MSEL について                | 18 |

| 5.4. MSEL 表                   | 20 |

| 6. タイムチャート                    | 25 |

| 6.1. 信号出力部ブロック図               | 25 |

| 6.2. タイムチャート                  | 26 |

| 7. LED                        | 29 |

| 7.1. LED の点灯条件                | 29 |

| 7.2. バージョン情報表示機能              | 30 |

| 8. “CONFIG.TXT”的準備            | 31 |

| 8.1. “CONFIG.TXT”とは           | 31 |

| 8.2. “CONFIG.TXT”サンプル         | 32 |

| 8.3. Commands                 | 33 |

| 8.4. D1,D2,PO の設定について         | 41 |

| 8.5. コマンドパラメータ デフォルト値         | 43 |

| 8.6. RBF データの生成方法             | 44 |

| 9. 機能詳細                       | 45 |

| 9.1. ワードアライナ機能                | 45 |

---

|                                                        |    |

|--------------------------------------------------------|----|

| 9.2. bit 連結による Multi FPGA Configuration 機能 .....       | 46 |

| 9.3. “CONFIG.TXT”による Multi FPGA Configuration 機能 ..... | 47 |

| 9.4. 外付け回路による最大 7 個の Multi FPGA Configuration 機能 ..... | 47 |

| 10. uSDCONF1A と uSDCONF1F の共存について .....                | 48 |

| 10.1. uSDCONF1F 用の基板に uSDCONF1A を実装する場合 .....          | 48 |

| 10.1.1. uSDCONF1F 用基板に uSDCONF1A を新規にアセンブリする場合 .....   | 48 |

| 10.1.2. uSDCONF1F 用ソケットが既に実装されている場合 .....              | 49 |

| 11. モジュールのソケットからの取り外しについて .....                        | 50 |

| 11.1. モジュール裏面 .....                                    | 50 |

| 12. 添付品 .....                                          | 52 |

| 13. VCCIO 電圧とシールの色 .....                               | 53 |

| 14. 発注型格 .....                                         | 53 |

| 15. 制約事項 .....                                         | 54 |

| 16. アップデート機能(順次対応予定) .....                             | 55 |

---

## 1. 機能・特徴

### 1.1. uSDCONF1A の機能・特徴

- ・ 本モジュールは microSD カードを媒体として、Windows システムによって Card に記憶されたバイナリデータを FPGA に転送してコンフィギュレーションを行う機能を供します。

- ・ microSD カードには、最大 2GB までの FAT16<sup>注1)</sup>でフォーマットされた Card を使用でき、容量の許す限り<sup>注2)</sup>バイナリデータを格納することができます。

- ・ microSD カードへのバイナリデータの書き込みは、Windows システムの Explorer 上で Drag & Copy するだけで簡単に行えます。 JTag ケーブルを接続する煩わしさがありません。

- ・ microSD カード上に格納する“CONFIG.TXT”の名称のアスキーキャラクタで記述された制御ファイルにより、FPGA に転送するバイナリデータの選択や、コンフィギュレーションに関する信号間の遅延量など、各種パラメータを指定することができ、専用のソフトを使うことなく、使い慣れたテキストエディタで編集するだけです。

- ・ “CONFIG.TXT”的先頭で、メーカ指定コマンドを入力すると、そのメーカに固有のパラメータ値をデフォルトとして設定することができます。

- ・ microSD カード上に格納されたバイナリデータは、“CONFIG.TXT”上で、バイナリデータ名と AREA[3:0]ピンによって指し示される 0 から F の 16 個の 16 進数文字と関連付けを行うことにより、AREA[3:0]ピンに接続されたロータリ-SW 設定により、最大 16 個のバイナリデータを瞬時に選択し、FPGA をコンフィギュレーションすることができます。(例えば #3 : data3.bin で SW 設定3と data3.bin を関連付けします。)

- ・ 本機能は、例えばデバッグの場面で開発段階の複数のバージョンのバイナリデータの動作比較や、デモの場面で複数のアプリケーションを瞬時に切り替えてデモンストレーションする場面などで威力を発揮します。

- ・ microSD カードとのインターフェースは 50MHz の HighSpeed モードで転送を行います。

- ・ FPGA への転送バス幅を 1bit と 8bit から選択することができます。(MODE ピン参照)

- microSD カードから FPGA への Passive Serial によるコンフィギュレーション。

- microSD カードから FPGA への FPP によるコンフィギュレーション。

- ・ FPGA への転送クロック DCLK は、“CONFIG.TXT”で指定することにより、下記の速度から選択可能です。

50MHz(デフォルト), 25MHz, 12.5MHz, 8.33MHz, 6.25MHz, 5MHz, 3.125MHz,

1.56MHz, 0.78MHz, 0.39MHz

- ・ ワードアライナ機能(#P:C0=1)を“CONFIG.TXT”上で有効にすることにより、被転送ファイルの先頭にある管理情報を読み飛ばし、データバイトが FFh が連続する領域まで読み飛ばして、最初の FFh から転送を開始することができます。現状、RBF の使用を推奨しているため、本パラメータは"0"を設定して下さい。

- ・ 0 から 15 回のコンフィギュレーションのリトライ回数が指定できます。

- ・ バイナリデータの先頭にプリアンブルを挿入することや、バイナリデータの最後にポストアンブルを可変長で挿入することができます。

- ・ リセット解除から nCONFIG の立ち上がりまでの間隔(D2 パラメータ)や、nSTATUS の立ち上がりから DCLK の出力開始までの間隔(D1 パラメータ)を指定することができます。

- ・ AES による暗号化と DeComp 機能に対応します。FPP モードでは、#P:C5=1 を設定することにより、1 バイトのデータに対し4回 DCLK を出力する×4機能も実装されています。これにより、お客様の大切な論理データをしっかりと保護した上で、microSD カードの可搬性をしっかりとご利用いただけます。

注 1) ファイル名は最大8文字+3文字までで、EFAT には対応していません。

注 2)ルートディレクトリに格納するため、FAT の構成上、最大 512 個の上限があります。

## 1.2. uSDCONF1F からの修正点

- ① microSD カードの電源制御が追加されました。これにより、パワーオンリセット時に必ず電源が初期化されるため、リセット信号のチャタリング等で microSD カードが INACT 状態に陥ることを回避できるようになりました。uSDCONF1F では INACT 状態に陥ったときは、電源を一旦 OFF するか、microSD カードを挿抜する必要がありましたが、uSDCONF1A ではリセット信号だけで INACT 状態から復帰できるようになりました。

- ② uSDCONF1F の前面方向の空きスペースを利用して、ピンの Dimension を変更することなく、新たに 2Pin 追加し、XCS0,XCS1 に割り当てました。(将来的に搭載する機能によっては別の信号に割り当てることもあります。)

これにより、SDCONF ソリューションのひとつのアドバンテージ機能である + 連結をご利用いただけます。

外付けの追加回路なしに、2つまでの FPGA に xCS 信号により選択コンフィギュレーションできます。

また、外付けに回路を追加することにより、最大 7 個までの FPGA に対して xCS 信号により選択コンフィギュレーションすることが可能です。

- ③ ~~搭載の制御用 FPGA の論理サイズが uSDCONF1F より 1.6 倍大きくなりました。これにより、今後のより高度な機能追加に、モジュールの買い替えなしに、論理データの変更だけでアップグレードが可能です。~~

(uSDCONF1F とのデータの互換性、価格面、ゲート使用率より、適用を見送りました。)

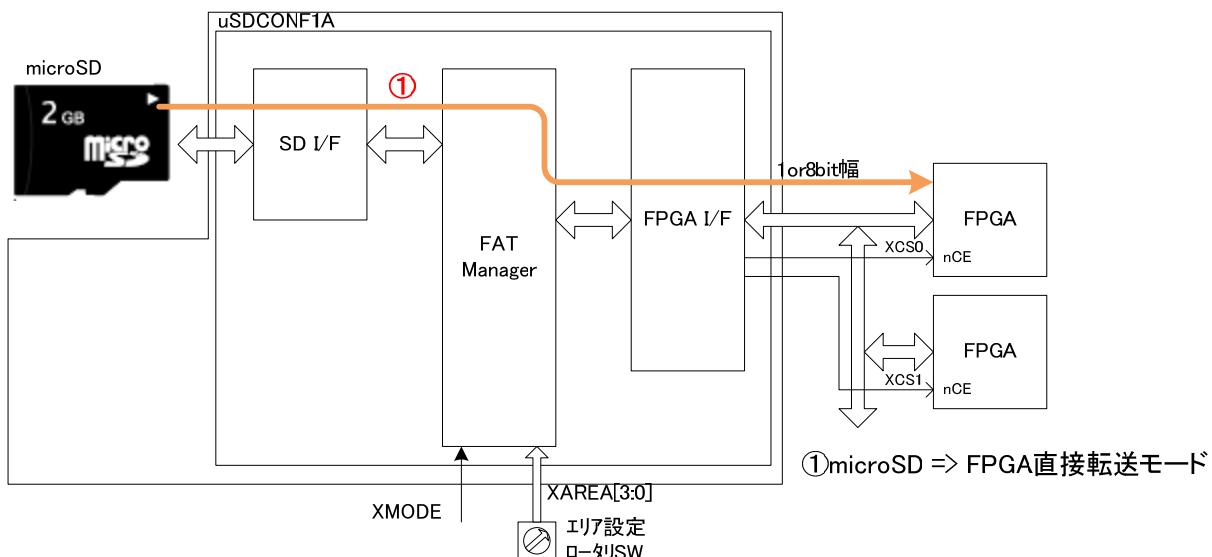

図 1.1 uSDCONF1A ブロックイメージ図

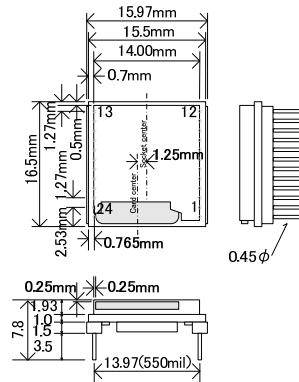

## 2. 形状

uSD-CONF1A モジュールの形状を掲載します。

図 2.1 uSDCONF1A 形状図

(1) uSDCONF1A の使用 pin は、MAC8 の OQ-11-5-12P。

(<http://www.mac8sdk.co.jp/mac8/pdf/OQ.pdf>)

ソケット実装の場合の推奨ソケットは、

MAC8 ME-10-10-12P(金メッキ品)、MAC8 ME-1-10-12P(スズメッキ品)。

(<http://www.mac8sdk.co.jp/mac8/pdf/MEMF.pdf>)

※製品には、MAC8 ME-10-10-12P(金メッキ品)が 2 個添付されます。

Neltron 2200Series

(<http://akizukidensi.com/download/2200-pinsocket.pdf>)

プリント板取付穴径は、直接実装、ソケット実装とも 0.6~0.7mm  $\phi$ 。

### 3. 電気特性

#### 3.1. 絶対定格

|                                       |        |    |        |

|---------------------------------------|--------|----|--------|

| Supply Voltage VCC3V                  | -0.2V  | to | 3.75V  |

| Supply Voltage VCCIO                  | -0.2V  | to | 3.75V  |

| Input or I/O Tristage Voltage Applied | -0.2V  | to | 3.75V  |

| Storage Temperature(Ambient)          | -65 °C | to | 150 °C |

#### 3.2. 推奨動作範囲

|                      |        |    |        |

|----------------------|--------|----|--------|

| Supply Voltage VCC3V | 3.135V | to | 3.465V |

| Supply Voltage VCCIO | 1.32V  | to | 3.465V |

| Ambient Temperature  | 0 °C   | to | 70 °C  |

#### 3.3. 消費電流

| 品目          |               | Typcal(実測) | Max   | 備考         |

|-------------|---------------|------------|-------|------------|

| Module 本体   | VCC(3.3V)     |            | 90mA  |            |

|             | VCCIO(3.3V 時) |            | 10mA  |            |

| microSD カード | VDD(3.3V)     |            | 100mA | 規格上の Max 値 |

| 合計          |               |            | 200mA |            |

表 3.3 消費電流表

#### 3.4. 電源シーケンス

- VCC3V と VCCIO の間には、電源シーケンスの指定はありません。

両者がともに動作許容範囲に入ったときに動作を開始します。

#### 3.5. リセットについて

- リセットは Low でアサートされる負論理入力です。

- FPGA 内部で、電源投入から立ち上がったときに、それを検出して、FPGA 内部の論理にリセットパルスを発行する機能を搭載しているため、リセット信号がなくても動作します。

- しかしながら、モジュールに対して、明示的にリセット信号を入れていただくことを推奨しており、リセット時間は、搭載している FPGA が電源安定から約 8msec で動作可能状態となるため、電源が安定してから 10msec 以上のリセット信号を入力することを推奨しています。

#### 4. Pin 機能表

uSDCONF1A モジュールのピン機能表を掲載します。

##### 4.1. uSDCONF1A ピン機能表

水平 1.27mm ハーフピッチ実装タイプのピン機能表を示します。

| Pin No. | Signal name | Dir | 内部 Pullup | Descriptions                           |

|---------|-------------|-----|-----------|----------------------------------------|

| 1       | XCS0        | O   |           | FPGA0 制御用チップセレクト信号                     |

| 2       | VCCIO       | —   |           | 入出力信号の VCCIO 電源入力。                     |

| 3       | XAREA0      | I   | 4.7K      | バイナリデータ選択用ロータリーSW(LSB)                 |

| 4       | VCC3V       | —   |           | 3.3V 電源入力                              |

| 5       | XAREA1      | I   | 4.7K      | バイナリデータ選択用ロータリーSW                      |

| 6       | GND         | —   |           | GND                                    |

| 7       | XAREA2      | I   | 4.7K      | バイナリデータ 選択用ロータリー SW                    |

| 8       | DONE        | I   | 330Ω      | FPGA DONE 信号                           |

| 9       | DCLK        | O   |           | FPGA DCLK 信号                           |

| 10      | nCONFIG     | O   | 4.7K      | FPGA nCONFIG 信号                        |

| 11      | XAREA3      | I   | 4.7K      | バイナリデータ選択用ロータリーSW(MSB)                 |

| 12      | nSTATUS     | O   | 4.7K      | FPGA nSTATUS 信号                        |

| 13      | XRST        | I   | 4.7K      | パワーオンリセット信号                            |

| 14      | D0 / SOUT   | O   |           | FPGA 8bit Parallel data0 / Serial data |

| 15      | D1          | O   |           | FPGA 8bit Parallel data1               |

| 16      | D2          | O   |           | FPGA 8bit Parallel data2               |

| 17      | D3          | O   |           | FPGA 8bit Parallel data3               |

| 18      | D4          | O   |           | FPGA 8bit Parallel data4               |

| 19      | GND         | —   |           | GND                                    |

| 20      | D5          | O   |           | FPGA 8bit Parallel data5               |

| 21      | D6          | O   |           | FPGA 8bit Parallel data6               |

| 22      | D7          | O   |           | FPGA 8bit Parallel data7               |

| 23      | XMODE       | I   | 4.7K      | モードピン H : PS / L : FPP                 |

| 24      | XCS1        | O   |           | FPGA1 制御用チップセレクト信号                     |

表 4.1 uSDCONF1A ピン機能表

注1) XAREA[3:0],XMODE, DONE,nCONFIG,nSTATUS の信号には内部に Pullup 抵抗が実装されており、外部で実装する必要はありません。

注2) XCS 制御する場合は、外部に終端抵抗が必要です。

## 4.2. XAREA 詳細

- “CONFIG.TXT”ファイル上で microSD カード上に格納されたバイナリデータと AREA[3:0]ピンによって指示される 0～F の 16 個の 16 進数文字と関連付けがなされます。

- XAREA[3:0]入力は負論理で入力され、正論理に反転された AREA[3:0]信号と“CONFIG.TXT”上の 16 進数文字と比較が行われ、一致した 16 進文字と関連付けられたバイナリデータをコンフィギュレーションデータとして選択します。

- 表 4.2 は負論理で入力された XAREA[3:0]の信号レベルと、それによって指示されるエリア番号 の対応表です。

- 外付けのロータリー-SW としてリアルコードタイプを実装すれば、ロータリー-SW の選択番号とエリア番号が一致します。

- ロータリー-SW の代わりに CPU から制御することも可能です。

| XAREA |   |   |   | 詳細    |

|-------|---|---|---|-------|

| 3     | 2 | 1 | 0 |       |

| H     | H | H | H | エリア 0 |

| H     | H | H | L | エリア 1 |

| H     | H | L | H | エリア 2 |

| H     | H | L | L | エリア 3 |

| H     | L | H | H | エリア 4 |

| H     | L | H | L | エリア 5 |

| H     | L | L | H | エリア 6 |

| H     | L | L | L | エリア 7 |

| L     | H | H | H | エリア 8 |

| L     | H | H | L | エリア 9 |

| L     | H | L | H | エリア A |

| L     | H | L | L | エリア B |

| L     | L | H | H | エリア C |

| L     | L | H | L | エリア D |

| L     | L | L | H | エリア E |

| L     | L | L | L | エリア F |

表 4.2 XAREA[3:0]とエリア番号表

## 5. 接続例

### 5.1. uSDCONF1A 接続例

#### 5.1.1. FPP/PS モード選択式

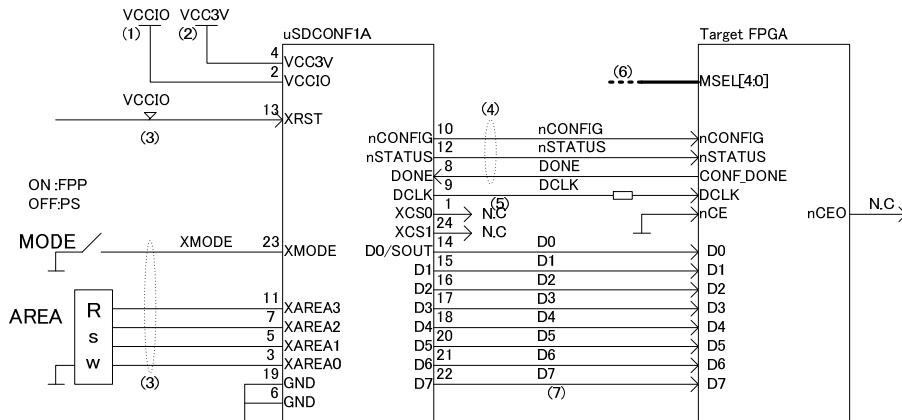

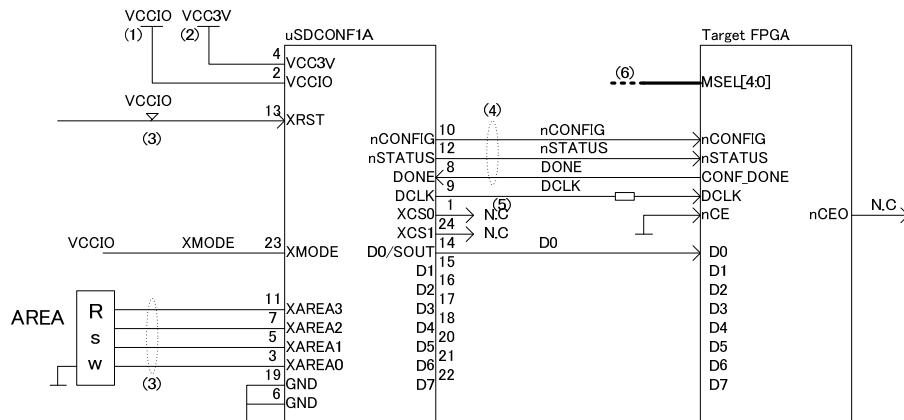

##### (1) FPGA と 1 対 1 接続の場合

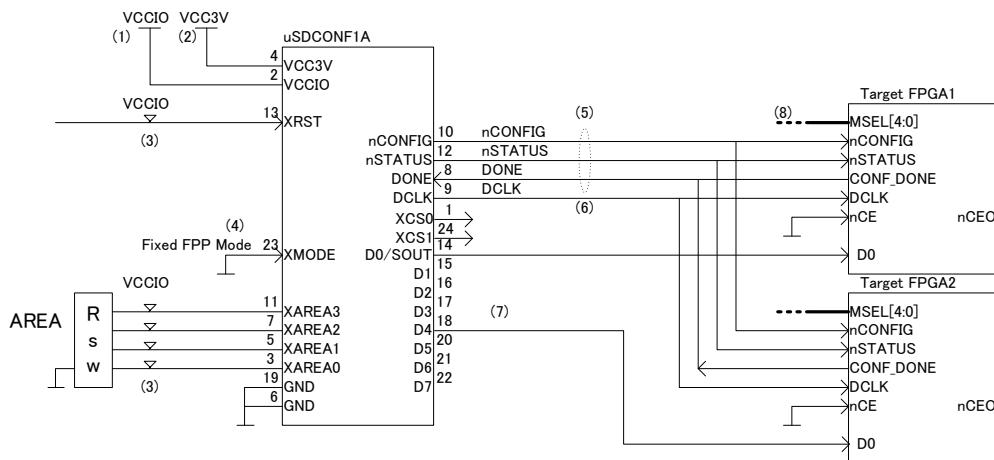

図 5.1.1.1 uSDCONF1A FPP / PS 選択式 1:1 接続例

- 注1) VCCIO は 3.3V～2.5V、1.8V に対応しており、3.0V の VCCIO に対応可能です。

VCCIO に 1.8V を使用する場合は、Module のデータを 1.8V 用に書き変える必要があります。

- 注2) 3.3V ± 5%(0.165V)が推奨入力電圧となります。

- 注3) XRST,XMODE,XAREA[3:0]ピンには、内部 Pullup 抵抗(4.7KΩ)が実装されており、外付けで終端抵抗を実装する必要はありません。

- 注4) nCONFIG,nSTATUS,DONE 信号には、Module 内部に Pullup 抵抗が実装されており、外部に実装する必要はありません。

ただし、uSDCONF1A をソケットから取り外して運用することがある場合は、外付けに終端抵抗を取り付けて下さい。

- 注5) DCLK は最短でレイアウトするようにして下さい。また、GND でシールドして下さい。

FPGA の近傍に、ダンピング抵抗を挿入できるようにしておくことを推奨します。

- 注6) XMODE ピンの論理と適合した MSEL[4:0]信号の設定値を選択して下さい。

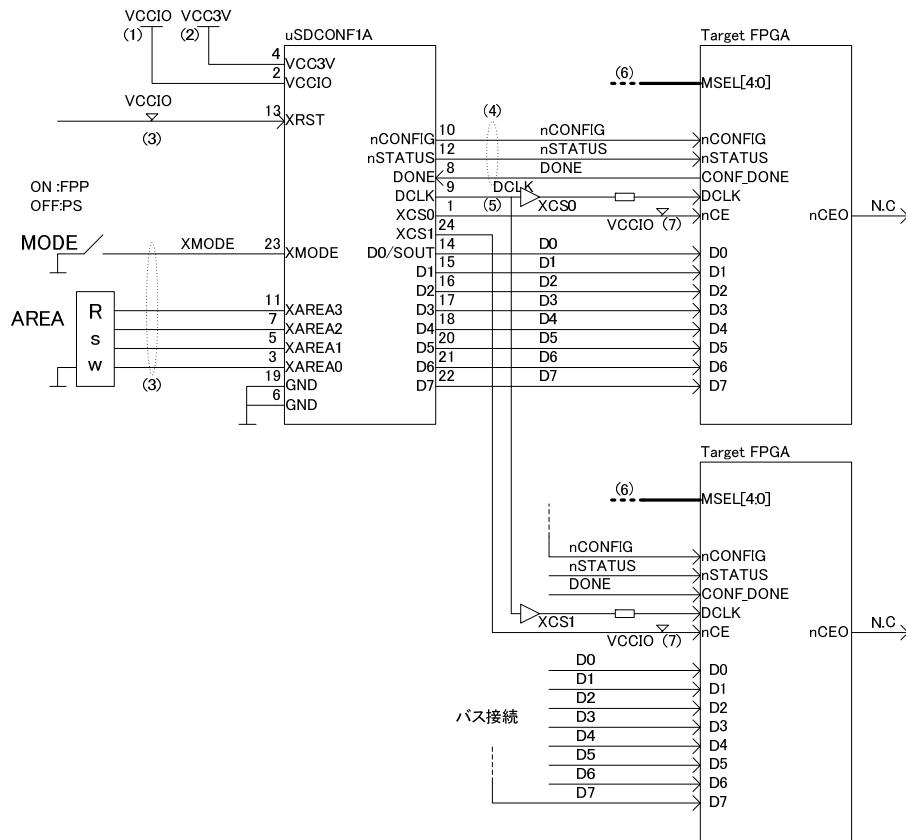

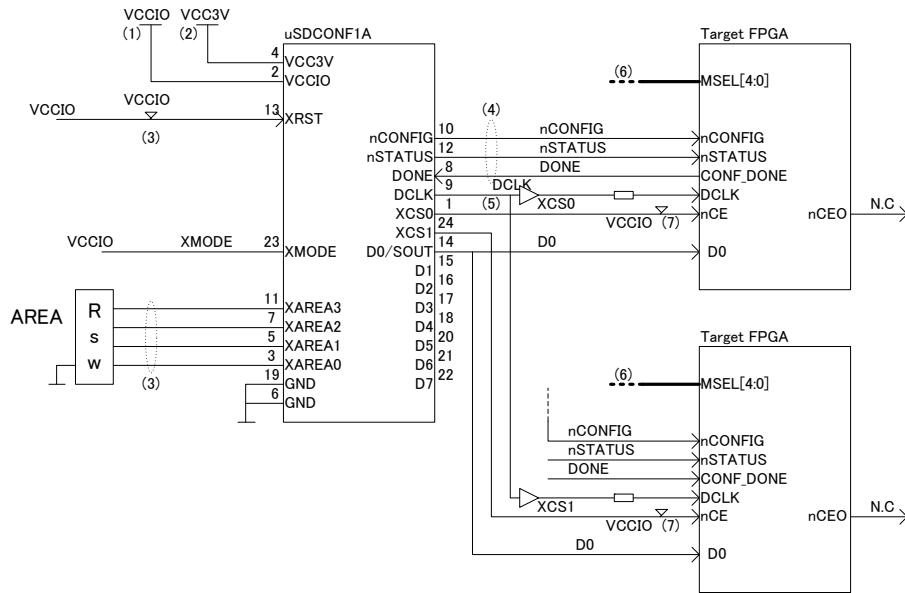

## (2) XCS 選択接続の場合

図 5.1.1.2 uSDCONF1A FPP / PS 選択式 1:2 接続例

- 注1) VCCIO は 3.3V～2.5V、1.8V に対応しており、3.0V の VCCIO に対応可能です。

VCCIO に 1.8V を使用する場合は、Module のデータを 1.8V 用に書き変える必要があります。

- 注2)  $3.3V \pm 5\% (0.165V)$  が推奨入力電圧となります。

- 注3) XRST,XMODE,XAREA[3:0]ピンには、内部 Pullup 抵抗( $4.7K\Omega$ )が実装されており、外付けで終端抵抗を実装する必要はありません。

- 注4) nCONFIG,nSTATUS,DONE 信号には、Module 内部に Pullup 抵抗が実装されており、外部に実装する必要はありません。

ただし、uSDCONF1A をソケットから取り外して運用することがある場合は、外付けに終端抵抗を取り付けて下さい。

- 注5) DCLK は最短でレイアウトするようにして下さい。また、GND でシールドして下さい。

FPGA の近傍に、ダンピング抵抗を挿入できるようにしておくことを推奨します。

- 注6) XMODE ピンの論理と適合した MSEL[4:0]信号の設定値を選択して下さい。

- 注7) XCS0,XCS1 を+連結で制御する若番の FPGA から順番に接続します。

それぞれの制御線には、FPGA の近傍に VCCIO で PullUp 抵抗( $4.7K\Omega$ )を接続して下さい。

### 5.1.2. PS モード固定

#### (1) FPGA と 1 対 1 接続の場合

図 5.1.2.1 uSDCONF1A PS 固定 1:1 接続例

- 注1) VCCIO は 3.3V～2.5V、1.8V に対応しており、3.0V の VCCIO に対応可能です。

VCCIO に 1.8V を使用する場合は、Module のデータを 1.8V 用に書き変える必要があります。

- 注2)  $3.3V \pm 5\%(0.165V)$  が推奨入力電圧となります。

- 注3) XRST,XMODE,XAREA[3:0]ピンには、内部 Pullup 抵抗( $4.7K\Omega$ )が実装されており、外付けで終端抵抗を実装する必要はありません。

- 注4) nCONFIG,nSTATUS,DONE 信号には、Module 内部に Pullup 抵抗が実装されており、外部に実装する必要はありません。

ただし、uSDCONF1A をソケットから取り外して運用することがある場合は、外付けに終端抵抗を取り付けて下さい。

- 注5) DCLK は最短でレイアウトするようにして下さい。また、GND でシールドして下さい。

FPGA の近傍に、ダンピング抵抗を挿入できるようにしておくことを推奨します。

- 注6) XMODE ピンの論理と適合した MSEL[4:0]信号の設定値を選択して下さい。

## (2) XCS 選択接続の場合

図 5.1.2.2 uSDCONF1A PS 固定 1:2 接続例

- 注1) VCCIO は 3.3V～2.5V、1.8V に対応しており、3.0V の VCCIO に対応可能です。

VCCIO に 1.8V を使用する場合は、Module のデータを 1.8V 用に書き変える必要があります。

- 注2) 3.3V ± 5%(0.165V)が推奨入力電圧となります。

- 注3) XRST,XMODE,XAREA[3:0]ピンには、内部 Pullup 抵抗(4.7KΩ)が実装されており、外付けで終端抵抗を実装する必要はありません。

- 注4) nCONFIG,nSTATUS,DONE 信号には、Module 内部に Pullup 抵抗が実装されており、外部に実装する必要はありません。

ただし、uSDCONF1A をソケットから取り外して運用することがある場合は、外付けに終端抵抗を取り付けて下さい。

- 注5) DCLK は最短でレイアウトするようにして下さい。また、GND でシールドして下さい。

FPGA の近傍に、ダンピング抵抗を挿入できるようにしておくことを推奨します。

- 注6) XMODE ピンの論理と適合した MSEL[4:0]信号の設定値を選択して下さい。

- 注7) XCS0,XCS1 を+連結で制御する若番の FPGA から順番に接続します。

それぞれの制御線には、FPGA の近傍に VCCIO で PullUp 抵抗(4.7KΩ)を接続して下さい。

## 5.2. uSDCONF1A Multi FPGA 接続例

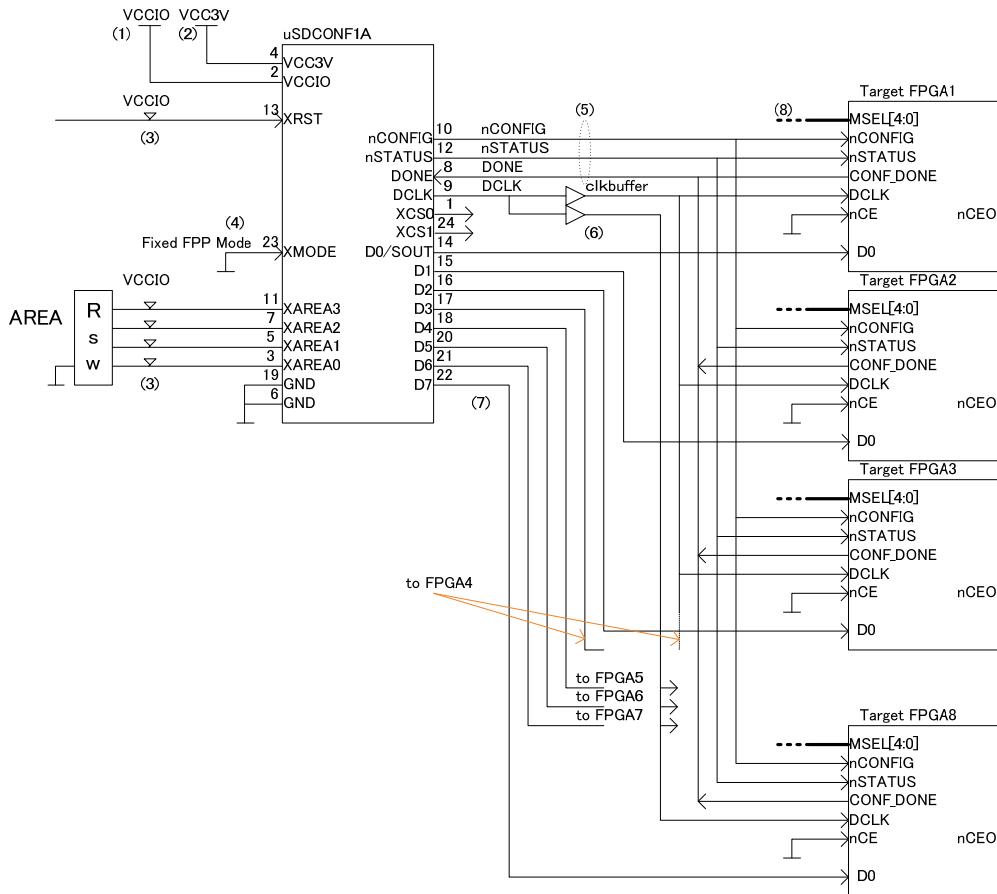

### (1) 8分割時

図 5.4.1 Multi FPGA x8 接続例

- 注1) VCCIO は 3.3V~2.5V、1.8V に対応しており、3.0V の VCCIO に対応可能です。

VCCIO に 1.8V を使用する場合は、Module のデータを 1.8V 用に書き変える必要があります。

- 注2)  $3.3V \pm 5\%(0.165V)$ が推奨入力電圧となります。

- 注3) XRST,XMODE,XAREA[3:0]ピンには、内部 Pullup 抵抗( $4.7K\Omega$ )が実装されており、外付けで終端抵抗を実装する必要はありません。

- 注4) 本モードでは XMODE ピンは FPP に、MSEL は PS に設定して下さい。

- 注5) nCONFIG,nSTATUS,DONE 信号には、Module 内部に Pullup 抵抗が実装されており、外部に実装する必要はありません。

- 注6) DCLK は最短でレイアウトするようにして下さい。また、GND でシールドして下さい。

FPGA4 個に対して 1 個の CLK バッファを挿入して下さい。

- 注7) FPGA の接続個数が 8 個に満たない場合、分割損が生じます。

- 注8) MSEL[3:0]の設定は動作モードに応じて選択して下さい。

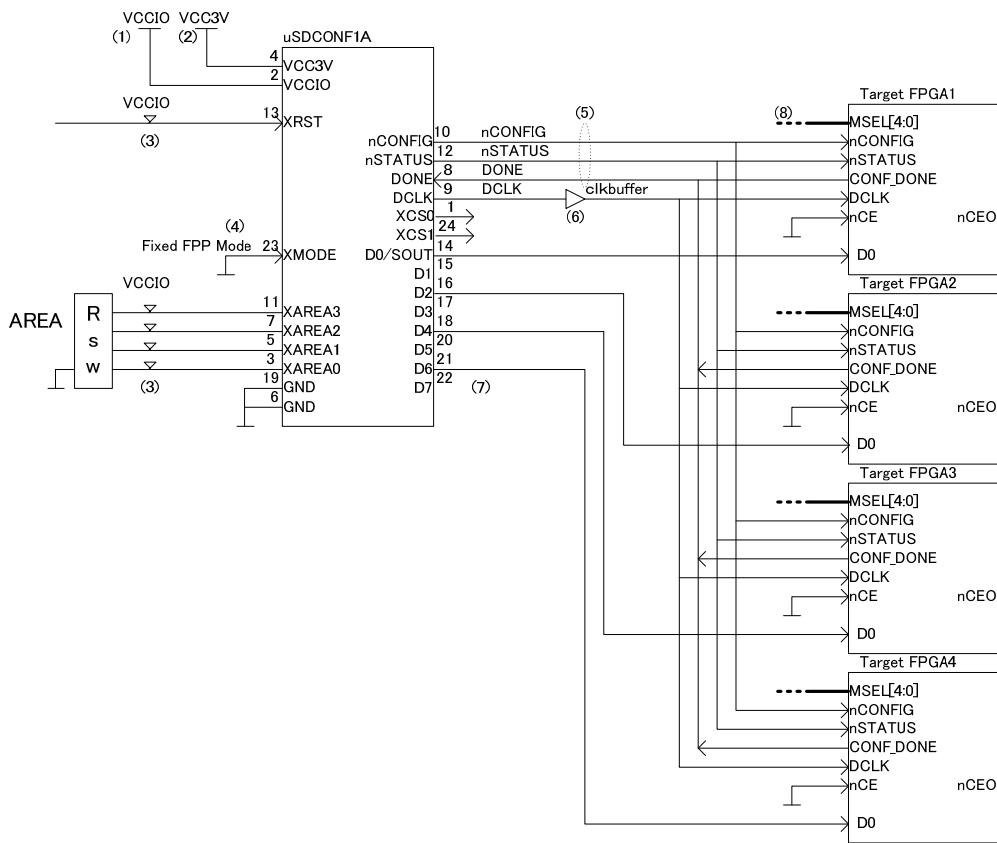

## (2) 4分割時

図 5.4.2 Multi FPGA x4 接続例

- 注1) VCCIO は 3.3V～2.5V、1.8V に対応しており、3.0V の VCCIO に対応可能です。

VCCIO に 1.8V を使用する場合は、Module のデータを 1.8V 用に書き変える必要があります。

- 注2)  $3.3V \pm 5\%(0.165V)$  が推奨入力電圧となります。

- 注3) XRST,XMODE,XAREA[3:0]ピンには、内部 Pullup 抵抗( $4.7K\Omega$ )が実装されており、外付けで終端抵抗を実装する必要はありません。

- 注4) 本モードでは XMODE ピンは FPP に、MSEL は PS に設定して下さい。

- 注5) nCONFIG,nSTATUS,DONE 信号には、Module 内部に Pullup 抵抗が実装されており、外部に実装する必要はありません。

- 注6) DCLK は最短でレイアウトするようにして下さい。また、GND でシールドして下さい。

FPGA4 個に対して 1 個の CLK バッファを挿入して下さい。

- 注7) MSEL[4:0]の設定は、動作モードに応じて選択して下さい。

- 注8) microSD カードの実効読出速度が 200Mbps に対して、 $50Mbps \times 2 = 100Mbps$  で、PS モードを 1 ～ 4 個において、書き込み速度を犠牲にすることなく効率的にコンフィギュレーションすることができます。

## (3) 2分割時

図 5.4.3 Multi FPGA x2 接続例

- 注1) VCCIO は 3.3V~2.5V、1.8V に対応しており、3.0V の VCCIO に対応可能です。VCCIO に 1.8V を使用する場合は、Module のデータを 1.8V 用に書き変える必要があります。

- 注2)  $3.3V \pm 5\%(0.165V)$  が推奨入力電圧となります。

- 注3) XRST,XMODE,XAREA[3:0]ピンには、内部 Pullup 抵抗( $4.7K\Omega$ )が実装されており、外付けで終端抵抗を実装する必要はありません。

- 注4) 本モードでは XMODE ピンは FPP に、MSEL は PS に設定して下さい。

- 注5) nCONFIG,nSTATUS,DONE 信号には、Module 内部に Pullup 抵抗が実装されており、外部に実装する必要はありません。

- 注6) DCLK は最短でレイアウトするようにして下さい。また、GND でシールドして下さい。FPGA4 個に対して 1 個の CLK バッファを挿入して下さい。

- 注7) MSEL[4:0]の設定は、動作モードに応じて選択して下さい。

- 注8) microSD カードの実効読出速度が 200Mbps に対して、50Mbps×2=100Mbps で、PS モードを 1~4 個において、書き込み速度を犠牲にすることなく効率的にコンフィギュレーションすることができます。

### 5.3. MSELについて

FPGAの大容量化、高機能化に伴ってMSELのビット数も増えています。

MSELの設定によって、コンフィギュレーションの転送モードや、インターフェース電圧、Supply\_voltageの立ち上がり時間、Securityなど、多岐に渡っています。

本章では本モジュールの観点から、これらの設定について簡単に説明します。

具体的な設定値については各FPGAのDataSheetかConfiguration Handbookをご参照いただくか、アルテラ担当営業様にお訊ね下さい。

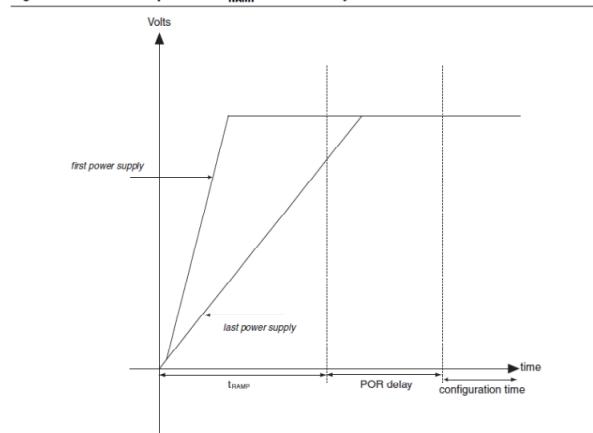

#### 5.3.1. POR Delay(FastとStandard)

FPGAには複数の電源電圧が供給されており、電源投入時、それらの電圧レベルはOperating電圧に到達するのに時間差が生じることが考えられます。

これらの全ての電源電圧がtRAMP(200us～100ms)以内にOperating電圧に到達しない電源電圧が存在する場合、POR Delayの設定によってこれを吸収する必要があります。

FPGAはPOR Delayが作動している間、nCONFIGをLowに保っています。

uSDCONF1Aモジュールは、モジュールに入力されるXRSTがリリースされた後、約1.7msec後にnCONFIGをリリースしますが、FPGA側がnCONFIGをLowにしている場合、これを検出してnCONFIGがFPGAからもリリースされてPullUP抵抗によりHighになるのを待ってからコンフィギュレーションを開始します。

“CONFIG.TXT”の#P:C1のpump ON機能はOFF(=0)(デフォルト)のままにしておく必要があります。

Figure 8-2. Relationship between t<sub>RAMP</sub> and POR Delay

図 5.5.1 Relationship between tRAMP and POR Delay

Table 9-2. Fast and Standard POR Delay Specification (Note 1)

| POR Delay | Minimum | Maximum |

|-----------|---------|---------|

| Fast      | 4 ms    | 12 ms   |

| Standard  | 100 ms  | 300 ms  |

表 5.5.1 Fast and Standard POR Delay Specification

### 5.3.2. Configuration Voltage

uSDCONF1A モジュールは VCCIO 電圧が 3.3V～2.5V、1.8V(データの書き換えが必要です。)に対応しています。

Stratix-V の 3.0V 電圧も VCCIO に 3.0V 電源電圧を印加することで動作します。

そのほか、1.5V や 1.2V についてもデータの書き換えによって対応することができます。(特注扱いとなります。)

### 5.3.3. FPP(x8,x16,x32)

uSDCONF1A モジュールは FPP の x8 に対応しています。

uSDCONF1A モジュールの XMODE ピンを Low に設定することにより FPP x8 モードが選択されます。

### 5.3.4. PS

uSDCONF1A モジュールは PS モードに対応しています。

uSDCONF1A モジュールの XMODE ピンを High に設定することにより PS モードが選択されます。

Multi FPGA 接続時、各 FPGA は MSEL を PS モードに設定する必要があります。

### 5.3.5. AS

uSDCONF1A モジュールは現状 AS モードには対応しておりません。

AS モードの組み込みは、同一ハードウェアにて対応検討中で、データのアップデートによって後日組み込むことが可能です。

詳しくはご相談下さい。

### 5.3.6. Remote

uSDCONF1A モジュール接続時、MSEL を Remote に設定することはありません。

### 5.3.7. Security

uSDCONF1A モジュールは、暗号化されたバイナリデータを特別に意識せず、通常のバイナリデータとして取り扱います。

FPGA に転送された暗号化されたバイナリデータは、FPGA の不揮発性領域に予め記憶された暗号 Key で復号化され、Key が一致した場合のみ復号化が成功し、コンフィギュレーションが正常に完了します。

FPP モードで AES を使用する場合は、#P:C5=1 の DCLK を 4 回出力するモードに設定する必要があります。

PS モードではその必要はありません。

### 5.3.8. Decomp

uSDCONF1A モジュールは、AES とセットで Decomp されたバイナリデータを取り扱うことが可能です。

FPP モードで Decomp を使用する場合は、#P:C5=1 の DCLK を 4 回出力するモードに設定する必要があります。

PS モードではその必要はありません。

#### 5.4. MSEL 表

各 FPGA の MSEL 表をピックアップします。

詳しくは各 FPGA の DataSheet か Configuration HandBook をご参照下さい。

古い種類の FPGA は、新規で採用されることはありませんが、過去に作成した評価ボードや試験用機材など、今も現役で使用されているものも数多くあると思われます。

これらの評価ボードや試験用機材などに改造を加えることによって uSD-COMF1 モジュールを実装することも可能です。

詳しくはご相談下さい。

Table 9-4. Configuration Schemes for Stratix V Devices (Part 1 of 2)

| Configuration Scheme | Decompression Feature | Design Security Feature | Configuration Voltage Standard (V) (2) | POR Delay (5) | MSEL[4..0] |

|----------------------|-----------------------|-------------------------|----------------------------------------|---------------|------------|

| FPP ×8               | Disabled              | Disabled                | 1.8/2.5/3.0                            | Fast          | 10100      |

|                      |                       |                         |                                        | Standard      | 11000      |

|                      | Disabled              | Enabled                 | 1.8/2.5/3.0                            | Fast          | 10101      |

|                      |                       |                         |                                        | Standard      | 11001      |

|                      | Enabled               | Optional (1)            | 1.8/2.5/3.0                            | Fast          | 10110      |

|                      |                       |                         |                                        | Standard      | 11010      |

|                      | Disabled              | Disabled                | 1.8/2.5/3.0                            | Fast          | 00000      |

|                      |                       |                         |                                        | Standard      | 00100      |

|                      | Disabled              | Enabled                 | 1.8/2.5/3.0                            | Fast          | 00001      |

| FPP ×16              |                       |                         |                                        | Standard      | 00101      |

|                      | Disabled              | Optional (1)            | 1.8/2.5/3.0                            | Fast          | 00010      |

|                      |                       |                         |                                        | Standard      | 00110      |

|                      | Disabled              | Disabled                | 1.8/2.5/3.0                            | Fast          | 01000      |

|                      |                       |                         |                                        | Standard      | 01100      |

|                      | Disabled              | Enabled                 | 1.8/2.5/3.0                            | Fast          | 01001      |

| FPP ×32              |                       |                         |                                        | Standard      | 01101      |

|                      | Disabled              | Optional (1)            | 1.8/2.5/3.0                            | Fast          | 01010      |

|                      |                       |                         |                                        | Standard      | 01110      |

|                      | Disabled              | Disabled                | 1.8/2.5/3.0                            | Fast          | 10000      |

|                      |                       |                         |                                        | Standard      | 10001      |

|                      | Disabled              | Enabled                 | 1.8/2.5/3.0                            | Fast          | 10010      |

| PS                   | Optional (1)          | Optional (1)            | 1.8/2.5/3.0                            | Fast          | 10011      |

| AS (x1, x4) (3)      | Optional (1)          | Optional (1)            | 3.0                                    | Fast          | 10010      |

|                      |                       |                         |                                        | Standard      | 10011      |

図 5.6.1 Stratix-V Configuration Schemes

Table 10-1. Configuration Schemes for Stratix IV Devices (Part 1 of 2)

| Configuration Scheme                                              | MSEL2 | MSEL1 | MSEL0 |

|-------------------------------------------------------------------|-------|-------|-------|

| Fast passive parallel                                             | 0     | 0     | 0     |

| Passive serial                                                    | 0     | 1     | 0     |

| Fast AS (40 MHz) (1)                                              | 0     | 1     | 1     |

| Remote system upgrade fast AS (40 MHz) (1)                        | 0     | 1     | 1     |

| FPP with design security feature and/or decompression enabled (2) | 0     | 0     | 1     |

図 5.6.2 Stratix-IV Configuration Schemes

Table 11-1. Stratix III Configuration Schemes

| Configuration Scheme                                                 | MSEL2 | MSEL1 | MSEL0 |

|----------------------------------------------------------------------|-------|-------|-------|

| Fast passive parallel (FPP)                                          | 0     | 0     | 0     |

| Passive serial (PS)                                                  | 0     | 1     | 0     |

| Fast AS (40 MHz) (1)                                                 | 0     | 1     | 1     |

| Remote system upgrade fast AS (40 MHz) (1)                           | 0     | 1     | 1     |

| FPP with design security feature, decompression, or both enabled (2) | 0     | 0     | 1     |

| JTAG-based configuration (4)                                         | (3)   | (3)   | (3)   |

図 5.6.3 Stratix-III Configuration Schemes

| Configuration Scheme                                                                         | MSEL3 | MSEL2 | MSEL1 | MSEL0 |

|----------------------------------------------------------------------------------------------|-------|-------|-------|-------|

| Fast passive parallel (FPP)                                                                  | 0     | 0     | 0     | 0     |

| Passive parallel asynchronous (PPA)                                                          | 0     | 0     | 0     | 1     |

| Passive serial (PS)                                                                          | 0     | 0     | 1     | 0     |

| Remote system upgrade FPP (1)                                                                | 0     | 1     | 0     | 0     |

| Remote system upgrade PPA (1)                                                                | 0     | 1     | 0     | 1     |

| Remote system upgrade PS (1)                                                                 | 0     | 1     | 1     | 0     |

| Fast AS (40 MHz) (2)                                                                         | 1     | 0     | 0     | 0     |

| Remote system upgrade fast AS (40 MHz) (2)                                                   | 1     | 0     | 0     | 1     |

| FPP with decompression and/or design security feature enabled (3)                            | 1     | 0     | 1     | 1     |

| Remote system upgrade FPP with decompression and/or design security feature enabled (1), (3) | 1     | 1     | 0     | 0     |

| AS (20 MHz) (2)                                                                              | 1     | 1     | 0     | 1     |

| Remote system upgrade AS (20 MHz) (2)                                                        | 1     | 1     | 1     | 0     |

| JTAG-based configuration (5)                                                                 | (4)   | (4)   | (4)   | (4)   |

#### 図 5.6.4 Stratix-II Configuration Schemes

| Table 11-2. Stratix & Stratix GX Device Configuration Schemes |       |       |       |  |

|---------------------------------------------------------------|-------|-------|-------|--|

| Description                                                   | MSEL2 | MSEL1 | MSEL0 |  |

| FPP configuration                                             | 0     | 0     | 0     |  |

| PPA configuration                                             | 0     | 0     | 1     |  |

| PS configuration                                              | 0     | 1     | 0     |  |

| Remote/local update FPP (1)                                   | 1     | 0     | 0     |  |

| Remote/local update PPA (1)                                   | 1     | 0     | 1     |  |

| Remote/local update PS (1)                                    | 1     | 1     | 0     |  |

| JTAG-based configuration (3)                                  | (2)   | (2)   | (2)   |  |

#### 図 5.6.5 Stratix & Stratix-GX Configuration Schemes

Table 8-3. Configuration Schemes for Cyclone IV GX Devices (EP4CGX15, EP4CGX22, and EP4CGX30 [except for F484 Package])

| Configuration Scheme         | MSEL2 | MSEL1 | MSEL0 | POR Delay | Configuration Voltage Standard (V) (1) |

|------------------------------|-------|-------|-------|-----------|----------------------------------------|

| AS                           | 1     | 0     | 1     | Fast      | 3.3                                    |

|                              | 0     | 1     | 1     | Fast      | 3.0, 2.5                               |

|                              | 0     | 0     | 1     | Standard  | 3.3                                    |

|                              | 0     | 1     | 0     | Standard  | 3.0, 2.5                               |

| PS                           | 1     | 0     | 0     | Fast      | 3.3, 3.0, 2.5                          |

|                              | 1     | 1     | 0     | Fast      | 1.8, 1.5                               |

|                              | 0     | 0     | 0     | Standard  | 3.3, 3.0, 2.5                          |

| JTAG-based configuration (2) | (3)   | (3)   | (3)   | —         | —                                      |

#### 図 5.6.6 Cyclone-IV GX(1/2) Configuration Schemes

Table 8-4. Configuration Schemes for Cyclone IV GX Devices (EP4CGX30 [only for F484 package], EP4CGX50, EP4CGX75, EP4CGX110, and EP4CGX150) (Part 1 of 2)

| Configuration Scheme | MSEL3 | MSEL2 | MSEL1 | MSEL0 | POR Delay | Configuration Voltage Standard (V) (1) |

|----------------------|-------|-------|-------|-------|-----------|----------------------------------------|

| AS                   | 1     | 1     | 0     | 1     | Fast      | 3.3                                    |

|                      | 1     | 0     | 1     | 1     | Fast      | 3.0, 2.5                               |

|                      | 1     | 0     | 0     | 1     | Standard  | 3.3                                    |

|                      | 1     | 0     | 1     | 0     | Standard  | 3.0, 2.5                               |

| PS                   | 1     | 1     | 0     | 0     | Fast      | 3.3, 3.0, 2.5                          |

|                      | 1     | 1     | 1     | 0     | Fast      | 1.8, 1.5                               |

|                      | 1     | 0     | 0     | 0     | Standard  | 3.3, 3.0, 2.5                          |

|                      | 0     | 0     | 0     | 0     | Standard  | 1.8, 1.5                               |

| FPP                  | 0     | 0     | 1     | 1     | Fast      | 3.3, 3.0, 2.5                          |

|                      | 0     | 1     | 0     | 0     | Fast      | 1.8, 1.5                               |

|                      | 0     | 0     | 0     | 1     | Standard  | 3.3, 3.0, 2.5                          |

|                      | 0     | 0     | 1     | 0     | Standard  | 1.8, 1.5                               |

#### 図 5.6.7 Cyclone-IV GX(2/2) Configuration Schemes

**Table 9-7.** Cyclone III Device Family Configuration Schemes *(Note 1)* (Part 1 of 2)

| Configuration Scheme                                                                        | MSEL |   |   |   | Configuration Voltage Standard (V)<br><i>(2),(3)</i> |

|---------------------------------------------------------------------------------------------|------|---|---|---|------------------------------------------------------|

|                                                                                             | 3    | 2 | 1 | 0 |                                                      |

| Fast Active Serial Standard (AS Standard POR)                                               | 0    | 0 | 1 | 0 | 3.3                                                  |

| Fast Active Serial Standard (AS Standard POR)                                               | 0    | 0 | 1 | 1 | 3.0/2.5                                              |

| Fast Active Serial Fast (AS Fast POR)                                                       | 1    | 1 | 0 | 1 | 3.3                                                  |

| Fast Active Serial Fast (AS Fast POR)                                                       | 0    | 1 | 0 | 0 | 3.0/2.5                                              |

| Active Parallel $\times 16$ Standard (AP Standard POR, for Cyclone III devices only)        | 0    | 1 | 1 | 1 | 3.3                                                  |

| Active Parallel $\times 16$ Standard (AP Standard POR, for Cyclone III devices only)        | 1    | 0 | 1 | 1 | 3.0/2.5                                              |

| Active Parallel $\times 16$ Standard (AP Standard POR, for Cyclone III devices only)        | 1    | 0 | 0 | 0 | 1.8                                                  |

| Active Parallel $\times 16$ Fast (AP Fast POR, for Cyclone III devices only)                | 0    | 1 | 0 | 1 | 3.3                                                  |

| Active Parallel $\times 16$ Fast (AP Fast POR, for Cyclone III devices only)                | 0    | 1 | 1 | 0 | 1.8                                                  |

| Passive Serial Standard (PS Standard POR)                                                   | 0    | 0 | 0 | 0 | 3.3/3.0/2.5                                          |

| Passive Serial Fast (PS Fast POR)                                                           | 1    | 1 | 0 | 0 | 3.3/3.0/2.5                                          |

| Fast Passive Parallel Fast (FPP Fast POR) <i>(4)</i>                                        | 1    | 1 | 1 | 0 | 3.3/3.0/2.5                                          |

| Fast Passive Parallel Fast (FPP Fast POR) (for Cyclone III devices only) <i>(4)</i>         | 1    | 1 | 1 | 1 | 1.8/1.5                                              |

| Fast Passive Parallel Fast (FPP Fast POR) (for Cyclone III LS devices only)                 | 0    | 0 | 0 | 1 | 1.8/1.5                                              |

| Fast Passive Parallel Fast (FPP Fast POR) with Encryption (for Cyclone III LS devices only) | 0    | 1 | 0 | 1 | 3.3/3.0/2.5                                          |

| Fast Passive Parallel Fast (FPP Fast POR) with Encryption (for Cyclone III LS devices only) | 0    | 1 | 1 | 0 | 1.8/1.5                                              |

**图 5.6.8 Cyclone-III Configuration Schemes****Table 13-1. Cyclone II Configuration Schemes**

| Configuration Scheme                | MSEL1      | MSEL0      |

|-------------------------------------|------------|------------|

| AS (20 MHz)                         | 0          | 0          |

| PS                                  | 0          | 1          |

| Fast AS (40 MHz) <i>(1)</i>         | 1          | 0          |

| JTAG-based Configuration <i>(2)</i> | <i>(3)</i> | <i>(3)</i> |

**图 5.6.9 Cyclone-II Configuration Schemes****Table 13-2. Selecting Cyclone Configuration Schemes**

| MSEL1 | MSEL0 | Configuration Scheme  |

|-------|-------|-----------------------|

| 0     | 0     | AS                    |

| 0     | 1     | PS                    |

| 0     | 1     | JTAG-based <i>(1)</i> |

**图 5.6.10 Cyclone Configuration Schemes**

Table 9-6. Configuration Schemes for Arria II GX Devices (Part 1 of 2)

| Configuration Scheme                                                 | MSEL3 | MSEL2 | MSEL1 | MSEL0 | POR Delay | Configuration Voltage Standard (V) (1) |

|----------------------------------------------------------------------|-------|-------|-------|-------|-----------|----------------------------------------|

| FPP                                                                  | 0     | 0     | 0     | 0     | Fast      | 3.3, 3.0, 2.5                          |

|                                                                      | 0     | 1     | 1     | 1     | Fast      | 1.8                                    |

| FPP with design security feature, decompression, or both enabled (2) | 0     | 0     | 0     | 1     | Fast      | 3.3, 3.0, 2.5                          |

|                                                                      | 1     | 0     | 0     | 0     | Fast      | 1.8                                    |

| PS                                                                   | 0     | 0     | 1     | 0     | Fast      | 3.3, 3.0, 2.5                          |

|                                                                      | 1     | 0     | 0     | 1     | Fast      | 1.8                                    |

|                                                                      | 1     | 0     | 1     | 0     | Standard  | 3.3, 3.0, 2.5                          |

|                                                                      | 1     | 0     | 1     | 1     | Standard  | 1.8                                    |

| AS with or without remote system upgrade                             | 0     | 0     | 1     | 1     | Fast      | 3.3                                    |

|                                                                      | 1     | 1     | 0     | 1     | Fast      | 3.0, 2.5                               |

|                                                                      | 1     | 1     | 1     | 0     | Standard  | 3.3                                    |

|                                                                      | 1     | 1     | 1     | 1     | Standard  | 3.0, 2.5                               |

图 5.6.11 Arria II GX Configuration Schemes

Table 11-1. Arria GX Configuration Schemes (Part 1 of 2)

| Configuration Scheme                                                  | MSEL3 | MSEL2 | MSEL1 | MSEL0 |

|-----------------------------------------------------------------------|-------|-------|-------|-------|

| Fast passive parallel (FPP)                                           | 0     | 0     | 0     | 0     |

| Passive parallel asynchronous (PPA)                                   | 0     | 0     | 0     | 1     |

| Passive serial (PS)                                                   | 0     | 0     | 1     | 0     |

| Remote system upgrade FPP (1)                                         | 0     | 1     | 0     | 0     |

| Remote system upgrade PPA (1)                                         | 0     | 1     | 0     | 1     |

| Remote system upgrade PS (1)                                          | 0     | 1     | 1     | 0     |

| Fast AS (40 MHz) (2)                                                  | 1     | 0     | 0     | 0     |

| Remote system upgrade fast AS (40 MHz) (2)                            | 1     | 0     | 0     | 1     |

| FPP with decompression feature enabled (3)                            | 1     | 0     | 1     | 1     |

| Remote system upgrade FPP with decompression feature enabled (1), (3) | 1     | 1     | 0     | 0     |

| AS (20 MHz) (2)                                                       | 1     | 1     | 0     | 1     |

| Remote system upgrade AS (20 MHz) (2)                                 | 1     | 1     | 1     | 0     |

图 5.6.12 Arria GX Configuration Schemes

Table 6-1. APEX II Configuration Schemes

| MSEL1 | MSEL0 | Configuration Scheme |

|-------|-------|----------------------|

| 0     | 0     | PS                   |

| 1     | 0     | FPP                  |

| 1     | 1     | PPA                  |

| (1)   | (1)   | JTAG Based (2)       |

图 5.6.13 APEX II Configuration Schemes

Table 7-1. APEX 20KE &amp; APEX 20KC Configuration Schemes

| MSEL1 | MSEL0 | Configuration Scheme |

|-------|-------|----------------------|

| 0     | 0     | PS                   |

| 1     | 0     | PPS                  |

| 1     | 1     | PPA                  |

| (1)   | (1)   | JTAG Based (2)       |

图 5.6.14 APEX 20KE &amp; KC Configuration Schemes

Table 8-1. Mercury, APEX 20K (2.5 V), ACEX 1K & FLEX 10K Configuration Schemes

| MSEL1 | MSEL0 | Configuration Scheme |

|-------|-------|----------------------|

| 0     | 0     | PS                   |

| 1     | 0     | PPS                  |

| 1     | 1     | PPA                  |

| (1)   | (1)   | JTAG Based (2)       |

図 5.6.15 APEX 20K ACEX 1K FLEX 10K Configuration Schemes

## 6. タイムチャート

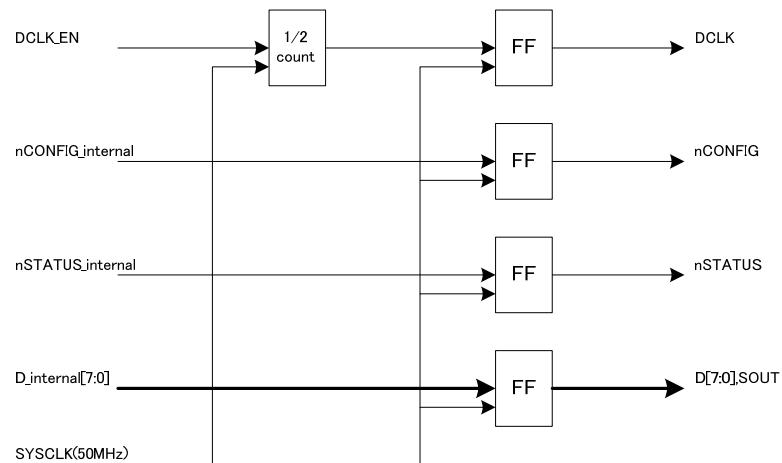

### 6.1. 信号出力部ブロック図

図 6.1 信号出力ブロック図

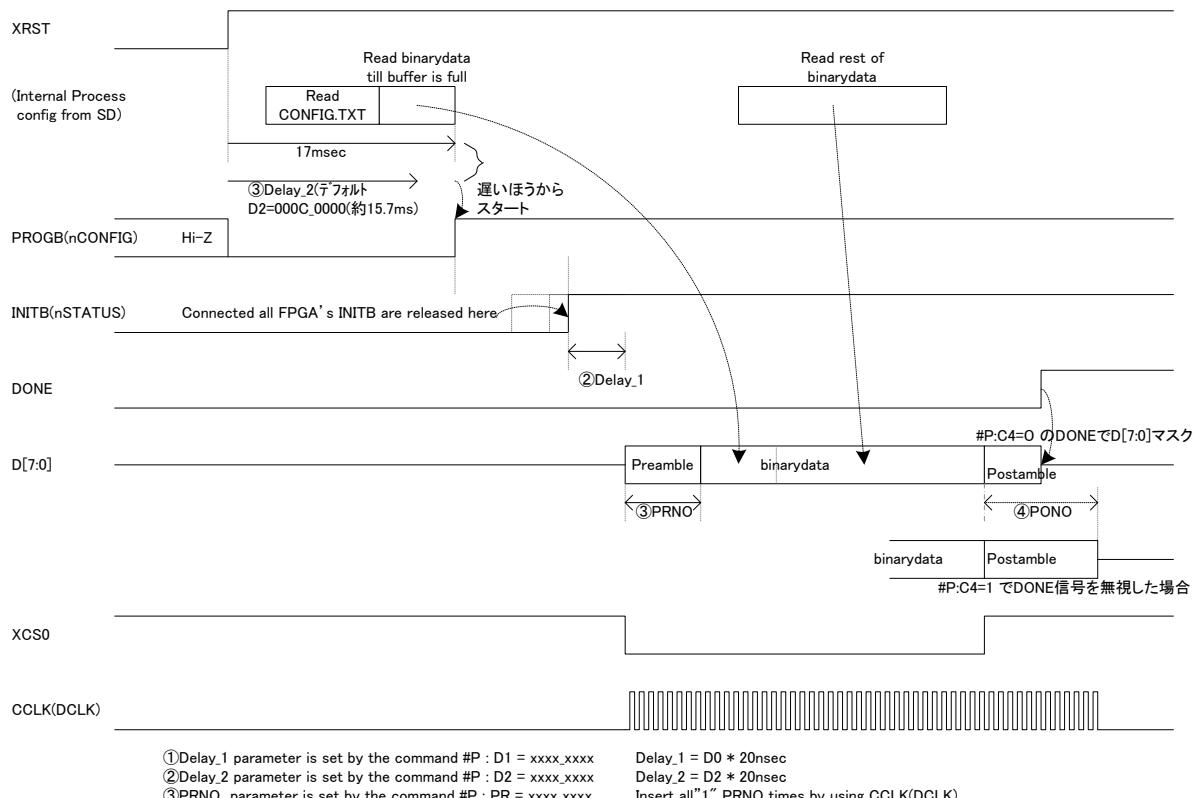

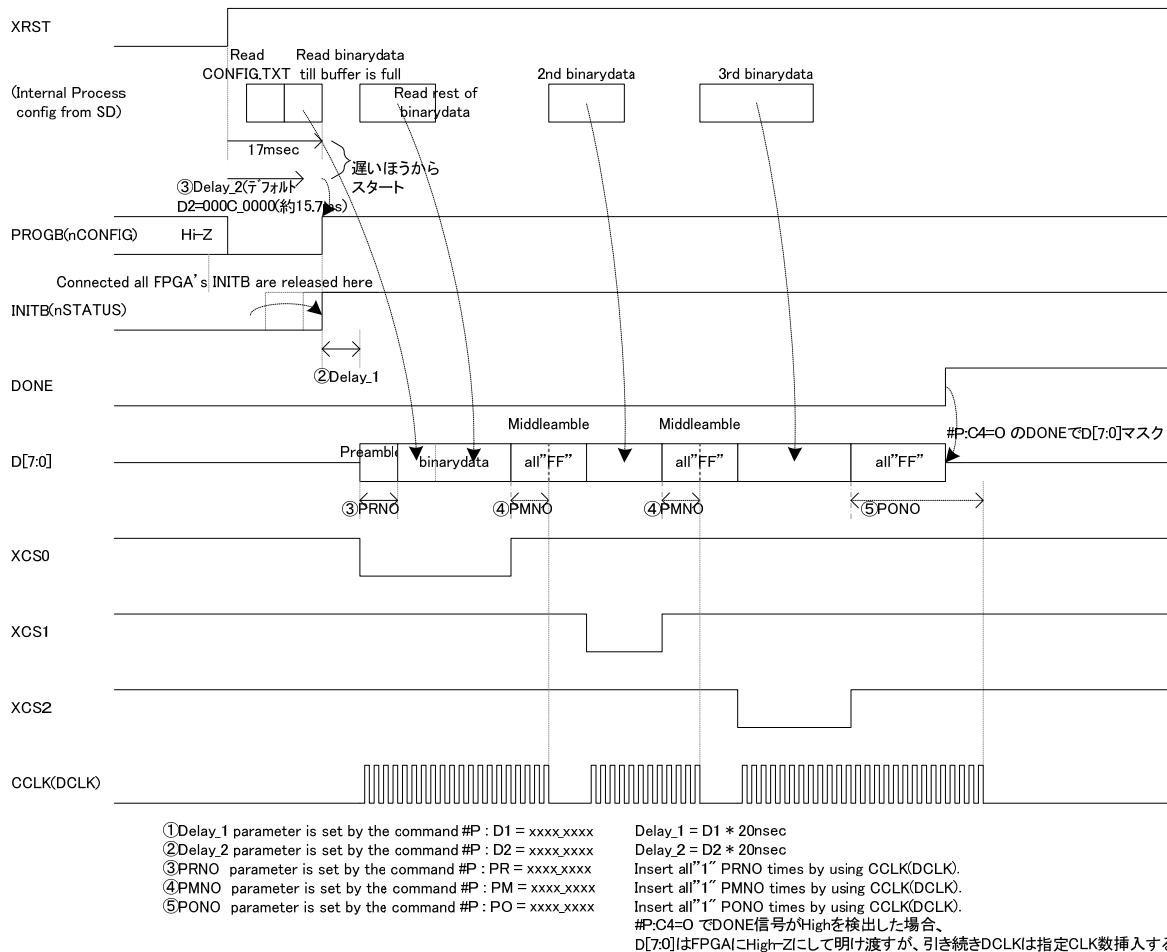

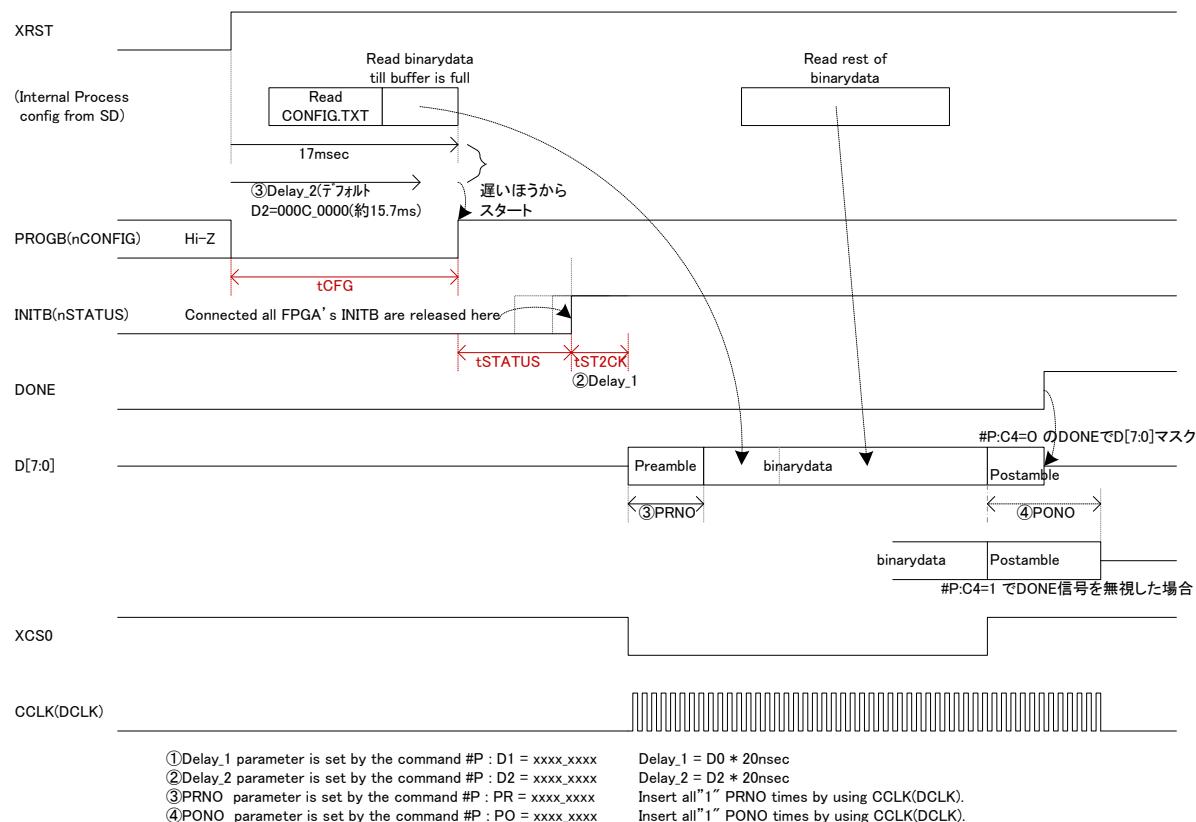

## 6.2. タイムチャート

### (1) SD カードから BinaryData を 1 個読み出し Config する場合

- XRST 信号は 5msec 以上アサートして下さい。また、チャタリングのない信号を入力して下さい。

- リセット期間中、nCONFIG は High-Z の状態となります。

- リセットが解除されたところから、D2 カウンタがカウントを開始し、config.txt で#P : D2= XXXX\_XXXX で設定したの設定時間を経過するか、SDCard からのデータの読み出し準備が出来た時点の、どちらか遅いほうの事象成立により nCONFIG が High-Z にリリースされ、外部 Pullup で High 論理が見えます。

- nSTATUS は、Ver1.800 より出力から入力方向に変更となりました。これに伴い、今まで D0 パラメータで nSTATUS のリリースまでの時間設定を行う必要がなくなり、パラメータは未使用となります。(指定しても読み飛ばされます。)

- 接続されている全ての FPGA の準備が整って、全ての FPGA が nSTATUS をリリースしたとき、外部 PullUp により nSTATUS は High 論理と見え、これをトリガに SDCONF は D1 カウンタのカウントを開始します。

- D1 カウンタの値が config.txt で設定した値か、デフォルト値に達したとき、XCS0 を Low に落とすと同時に Preamble 信号を#P : PR=XXXX\_XXXX で設定した値だけ DCLK とともに Data バスに ALL"1" 信号を出力します。(アルテラ FPGA では Preamble を入れる必要はなく、指定せずに、デフォルト値の PR=0000\_0000 で運用して下さい。)

- バイナリデータが送出し終わると、XCS0 を High に戻し、#P:PR=XXXX\_XXXX で設定した値分、DCLK をを出力するとともに、Data バスに Postamble として ALL"1"を出力します。

- もし、#P:C4=0(デフォルト)設定の場合、CONF\_DONE 信号が High になったことを検出して、Data バスを High-Z に開放して端子を FPGA に空け渡します。ただし、DCLK については、PO で設定されたクロック数、最後まで出力します。#P:C4=1 に設定された場合、CONF\_DONE 信号によらず、PO の設定値分、Data バスに ALL"1"を出し続けます。

## (2) SD カードから BinaryData を3個読み出し転送の場合

- XRST 信号は 5msec 以上アサートして下さい。また、チャタリングのない信号を入力して下さい。

- リセット期間中、nCONFIG は High-Z の状態となります。

- リセットが解除されたところから、D2 カウンタがカウントを開始し、config.txt で#P : D2= XXXX\_XXXX で設定したの設定時間を経過するか、SDCard からのデータの読み出し準備が出来た時点の、どちらか遅いほうの事象成立により nCONFIG が High-Z にリリースされ、外部 Pullup で High 論理が見えます。

- nSTATUS は、Ver1.800 より出力から入力に変更となりました。これに伴い、今まで D0 パラメータで nSTATUS のリリースまでの時間設定を行う必要がなくなり、パラメータは未使用となります。(指定しても読み飛ばされます。)

接続されている全ての FPGA の準備が整って、全ての FPGA が nSTATUS をリリースしたとき、外部 PullUp により nSTATUS は High 論理と見え、これをトリガに SDCONF は D1 カウンタのカウントを開始します。

- D1 カウンタの値が config.txt で設定した値か、デフォルト値に達したとき、XCS0 を Low に落とすと同時に Preamble 信号を#P : PR=XXXX\_XXXX で設定した値だけ DCLK とともに Data バスに ALL"1" 信号を出力します。(アルテラ FPGA では Preamble を入れる必要はなく、指定せずに、デフォルト値の PR=0000\_0000 で運用して下さい。)

- 1 個目のバイナリデータが送出し終わると、XCS0 を High に戻し、#P:PM=XXXX\_XXXX で設定した値分、DCLK を出力するとともに、Data バスに ALL"1" を出力します。

- PM パラメータは、バイナリデータと次のバイナリデータとの間 (Middle) に ALL"1" を PM で指定した個数

DCLK を挿入します。(Middle amble)

PM で設定した値分 DCLK を出し終えると、次のデータの送信準備ができるまで、DCLK は停止した状態で、Data バスに ALL"1"を出し続けます。

- PM のカウントが終了して、データの準備ができると、次の XCS1 を Low に落とすと同時にバイナリデータを送出し始めます。

このとき、PM で指定した DCLK の挿入が、Preamble と Postamble の代わりとなります。

- 最後のバイナリデータを送信し終わると、PO で指定したカウンタ分 DCLK と Data バスに ALL"1"を出力します。

- もし、#P:C4=0(デフォルト)設定の場合、DONE 信号が High になったことを検出して、Data バスを High-Z に開放して端子を FPGA に空け渡します。ただし、DCLK については、PO で設定されたクロック数、最後まで出力します。#P:C4=1 に設定された場合、DONE 信号によらず、PO の設定値分、Data バスに ALL"1"を出し続けます。

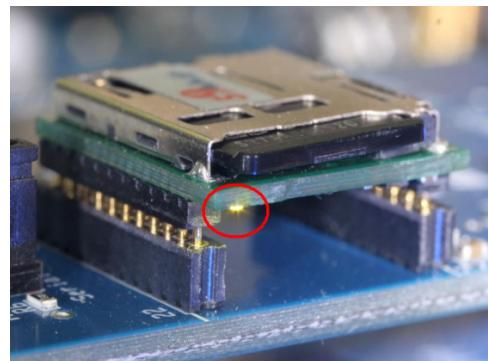

## 7. LED

- uSDCONF1A にはモジュールの状態を表示するための LED(緑)が実装されています。

図 7.1 LED の実装位置

### 7.1. LED の点灯条件

- LED の点灯条件は以下の通りです。

| LED 状態                                     | 条件                                                                                                                                                                                                                                                                                                                                                                                                         |

|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 点灯                                         | Passive Serial モードで microSD カードよりデータを転送している間。<br>FPP モードで microSD カードよりデータを転送している間。                                                                                                                                                                                                                                                                                                                        |

| 点滅<br>167msec 点灯 +<br>167msec 消灯の<br>繰り返し。 | Passive Serial / FPP モードで microSD カードのルートディレクトリに“CONFIG.TXT”を認識できなかった場合。<br>原因：“CONFIG.TXT”ファイルが存在しない。<br>スペルが間違っている。<br>“CONFIG.TXT”ファイルが 8 文字以上のキャラクタとして登録されている場合。(microSD カード上でコピペし、rename した場合など。)<br><br>Passive Serial / FPP モードで“CONFIG.TXT”によって指定されたバイナリデータがルートディレクトリ上で認識できなかった場合。<br>原因：バイナリデータが存在しない。<br>スペルが間違っている。<br>バイナリデータが 8 文字以上のキャラクタとして登録されている場合。(microSD カード上で 8 文字以下に rename した場合など。) |

| 無点灯                                        | microSD カードが挿入されていない場合は消灯のままです。                                                                                                                                                                                                                                                                                                                                                                            |

| バージョン情報<br>表示                              | “CONFIG.TXT”で#P : C9 = 1 が指定されている場合。<br>上記の microSD カードが挿入されていない場合を除き、モードに関係なくバージョン情報が表示されます。                                                                                                                                                                                                                                                                                                              |

表 7.1 LED 点灯条件

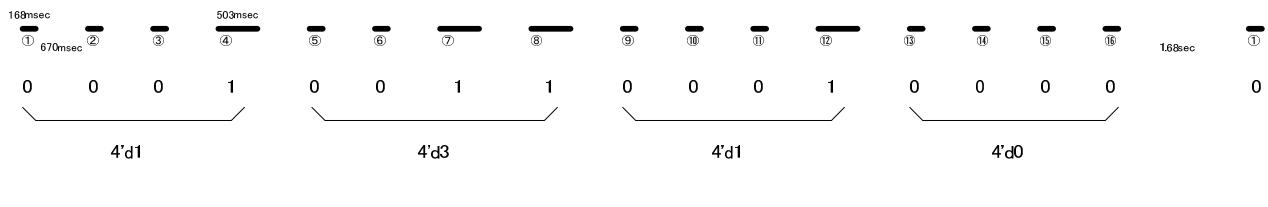

## 7.2. バージョン情報表示機能

- “CONFIG.TXT”で #P : C9 = 1 を指定することにより、本モジュールの裏面に実装された LED(図 7.1 参照)の点滅により、モジュールのバージョン情報を表示させることができます。

- バージョン情報は、16 ビットからなり、4 ビット毎に分割した 4 枠のヘキサデータとして表現されます。

- モールス信号のように、LED の点灯時間の長短で“0”と“1”的二進情報を表現します。

- 168msec の短い点灯と 670msec の消灯で“0”を表します。

- 503msec の 3 倍長い点灯と 670msec の消灯で“1”を表します。

- 16 回の点灯のあと、1.6sec の消灯区間で一巡したことを意味します。

- 一周目は無意味なデータが入っているため読み飛ばして、二周目から読みだして下さい。

- 図 7.2 は LED の点滅を時間系列上に太線で表した例です。時間は左から右に経過し、太線が点灯中を表し、太線と太線の間の空白は消灯区間を表します。

- LED の点滅の長さを見ながら“0”, “1”をメモしていくと、16 個の 2 進の繰り返しとなります。

- 4 個ずつ区切ってバイナリをヘキサに変換すると、“1310”となります。

- これは現在の最新情報で、バージョンが“1h”、リビジョンが“31h”、サフィックスが“0h”であることを示します。

- バージョン情報は、大規模な変更が行われない限りこの数値が続きます。

- リビジョン情報は、論理の修正があるアップデートが行われるとインクリメントします。

- サフィックス情報は、同一論理において、インターフェース条件の異なるものが存在する場合に割り振られます。

Version 1. 310

図 7.2 LED 点滅例

## 8. “CONFIG.TXT”的準備

### 8.1. “CONFIG.TXT”とは

- microSD カードから FPGA へ直接コンフィギュレーションを行う場合、若しくは、microSD カードから NandFlash へデータを転写する場合に参照されるテキストファイルです。

- ファイル名は 半角アスキーの“**CONFIG.TXT**”(小文字、大文字小文字混在も可)に固定化されており、microSD カードのルートディレクトリに置く必要があります。

- “CONFIG.TXT”ファイルには、ビットファイル名や、各種パラメータを列記します。

- “CONFIG.TXT”ファイルで取り扱えるキャラクタは、**半角アスキーコードのみ**です。

- “CONFIG.TXT”ファイル内のコマンドは、大文字、小文字、両者混在で記載してもかまいません。

例えば PO(ピーオー)など、Po と記載して 0(ゼロ)との紛らわしさを避けることができます。

漢字やひらがなは使えません。全角の空白の混入には注意して下さい。

## 8.2. “CONFIG.TXT”サンプル

- microSD カードの root ディレクトリに、“CONFIG.TXT”(小文字も可)の名称のファイルを準備する必要があります。

```

// This file is config test          //single'/' indicates comment out. '//' is familiar to verilog user.

#M : A                           //A: Altera

#S : 1                           //0:50M(def),1:25M,2:12.5M,3:8.333M,4:6.25M,5:5M

//6:3.125M,7:1.56M,8:0.78M,9:0.39M,F:Active

//Swap parameters

#P : SS = 1                      //Swap bit

//#P : SB = 0                      //Swap byte

//#P : SW = 0                      //Swap word

//Preamble/Postamble parameters

#P : PR = 0000_0040              //Preamble insert Number by counting DCLK

#P : Po = 0000_8000              //Postamble insert Number by counting DCLK

//Delay parameters

#P : D0 = 0000_0100              //delay Number from nCONFIG to nSTATUS by counting 50MCLK

#P : D1 = 0000_0100              //delay Number from nSTATUS to DCLK by counting 50MCLK.

//Command parameters

#P : C0 = 1                      //WordAligner

#P : C1 = 0                      //nCONFIG,nSTATUS Pump ON

#P : C2 = 0                      //MultiFPGA 2to1 x 4

#P : C3 = 0                      //MultiFPGA 4to1 x 2

//#P : C9 = 1                      //Version Information display on LED.

//Binary data area

//TEST_LED.RBF                    //If binary file appear without "#n :",

//the binary file will select immediately.

#0 : TESTLED0.RBF                //rbf file

#1 : TESTLED1.POF                //pof file

#2 : TESTLED2.RBF                //rbf file

#3 : TESTLED3.POF                //pof file

#4 : TESTLED4.RBF

#5 : testled5.rbf

...

#F : TESTLED5.rbf

//end

```

図 8.2. “CONFIG.TXT”サンプル

### 8.3. Commands

#### (a) “/” (“slash”)

- コメントアウトを行います。

- 行中に “/” を検出すると、“CR”までのそれ以降の文字列をコメントとして読み飛ばします。

- サンプルでは、Verilog の慣例に従い、“//”で表記しています。

#### (b) #M : A/L/X

- Maker を指定します。デフォルトはありません。

- 本パラメータを指定することにより、7.4(2)のパラメータが自動で設定されます。

- デフォルトパラメータ値を変更したい場合、本コマンドの後に変更したいパラメータのコマンドを記述して下さい。設定値が上書き修正されます。

- PO パラメータなどの FPGA によって異なるパラメータだけ設定して下さい。

#### (c) #S : 0/1/2/3/4/5/6/7/8/9/F

- FPGA 側の DCLK の速度を指定します。

|                  |              |

|------------------|--------------|

| 0 : 50MHz(デフォルト) | 6 : 3.125MHz |

| 1 : 25MHz        | 7 : 1.56MHz  |

| 2 : 12.5MHz      | 8 : 0.78MHz  |

| 3 : 8.333MHz     | 9 : 0.39MHz  |

| 4 : 6.25MHz      | A～F : 未定義    |

| 5 : 5MHz         |              |

#### (d) #P : SS = 0/1

- シリアルモード転送時(XMODE ピン = High)、D0(SOUT)ピンに最初に出力されるビットの MSB / LSB の出力順番の選択を行います。

- 0 : MSB ファースト

1 : LSB ファースト(デフォルト)

- 本コマンドはシリアル転送のときのみ有効で、次の #P:SB コマンドの影響は受けません。

#### (e) #P : SB = 0/1

- バイト単位内で、MSB と LSB を入れ替えます。

本モジュールでは、通常、microSD カード上のバイナリデータのバイト単位の MSB が D7 ピンに、LSB が D0 ピンに出力されます。

本パラメータを ON にすると、バイト内で MSB と LSB がスワップされます。

- 0 : Byte Swap 無し (デフォルト)

1 : Byte Swap 有り

- 本コマンドはパラレル転送のときのみ有効で、前記の #P:SS コマンドには影響を与えません。

## (f) #P : SW = 0/1

- ・ 本モジュールでは、16bit、32bit のバス幅指定ができないため、指定しても機能しません。

- ・ Full バージョンのソリューションでは、MODE[3:0]ピンにより、FPGA のバスを 32bit/16bit/8bit/1bit から選択できますが、32bit バス、16bit バス時に有効な設定で、Word 内を Byte 単位でスワップすることができます。

- ・ FPGA バスが 32bit モードのとき、下記のように選択されます。

0 : Word Swap 無し

1 : [31:24] => [ 7: 0]

[23:16] => [15: 8]

[15: 8] => [23:16]

[ 7: 0] => [31:24]

- ・ FPGA バスが 16bit モードのとき、下記のように選択されます。

0 : Word Swap 無し

1 : [15: 8] => [ 7: 0]

[ 7: 0] => [15: 8]

## (g) #P : PR = xxxx\_xxxx

- ・ バイナリデータを FPGA に送信する前に、プリアンブルデータとして Data Bus を All“1”にした状態で、指定回数の DCLK を出力します。

- ・ 指定は 16 進数で行い、8 衔全てを指定する必要があります。

0000\_0000 から FFFF\_FFFF まで指定できます。

- ・ 16 進数間にアンダーバー“\_”を任意に入れることができます。

- ・ 0000\_0000 を指定すると、プリアンブルは出力されません。

- ・ 指定がない場合のデフォルトは 0000\_0000 です。(アルテラ FPGA はプリアンブルは不要なため、指定せず、デフォルトの 0000\_0000 として下さい。)

- ・ Altera の RBF ファイルの先頭にある 32 個の FF についてはデータと認識して出力されますので、本パラメータの指定の有無に係わらず出力されます。

(h) #P : PO = xxxx\_xxxx

- バイナリデータを送信終了後、FPGA 内部の Initialization が完了させるため、所定の DCLK を送り続ける必要があります。

- バイナリデータを FPGA に送信した後に、ポストアンブルデータとして Data Bus を All“1”にした状態で、指定回数の DCLK を出力します。

- 指定は 16 進数で行い、8 衔全てを指定する必要があります。

- 0000\_0000 から FFFF\_FFFF まで指定できます。

- 16 進数間にアンダーバー“\_”を任意に入れることができます。

- 0000\_0000 を指定すると、ポストアンブルは出力されません。

- FFFF\_FFFF を指定すると、DCLK は停止せずに出力されつづけます。

この場合、#R コマンドは機能しません。

- 何も指定しないと、デフォルトとして 0000\_1000 が設定されます。

- DCLK は DONE 信号がアクティブになっても出力され続けます。

- Data バスはポストアンブル送信途中でも、DONE 信号がアクティブになると High-Z に開放されます。(DONE 信号を無視するためには、#p:C4=1 を設定して下さい。)

(i) #P : PM = xxxx\_xxxx

- 十連結で、複数のバイナリデータを FPGA に送信する場合に、バイナリデータを送信し終わって、次のバイナリデータを送信する際に、Data Bus を All“1”にした状態で、PM で指定した回数 DCLK を出力します。

- 指定は 16 進数で行い、8 衔全てを指定する必要があります。

- 0000\_0000 から FFFF\_FFFF まで指定できます。

- 16 進数間にアンダーバー“\_”を任意に入れることができます。

- 0000\_0000 を指定すると、ミドルアンブルは出力されません。

- 何も指定しないと、デフォルトとして 0000\_1000 が設定されます。

- Data バスはミドルアンブル送信後も、次のバイナリデータ送信開始まで ALL"1"を出力し続けます。

④#P : DR = xxxx\_xxxx => #P:D2=xxxx\_xxxx に変更。

- XRST が High になって nCONFIG を High にするまでの間隔を指定します。

- 指定は 16 進数で行い、8 衔全てを指定する必要があります。

- 0000\_0000 から FFFF\_FFFF まで指定できます。

- 16 進数間にアンダーバー“\_”を任意に入れることができます。

- 設定数値 × 20nsec がディレイ時間となります。

- SD カードからのコンフィギュレーションの場合、SD カード読み出し準備時間の 17msec より短い時間を設定した場合、機能しません。

- Nand からのコンフィギュレーションの場合、SD カード読み出し準備時間による待ちが存在しないため、本パラメータが有効になります。

- デフォルトは 000D\_0000 が設定され、約 17msec の遅延が挿入され、SD カード読み出し準備時間

による遅延による動作と、ほぼ等価となります。

(f) #P : D0 = xxxx\_xxxx

- ROM バージョン V1.800 より nSTATUS 信号が出力から入力に変更となりました。これに伴い、nSTATUS の出力の時間タイミングを規定する D0 パラメータは削除されました。

- 指定されても読み飛ばされ、エラーとはなりません。

- ~~nCONFIG がリリースされて nSTATUS がリリースされるまでのディレイ間隔を指定します。~~

- ~~指定は 16 進数で行い、8 衔全てを指定する必要があります。~~

- ~~0000\_0000 から FFFF\_FFFF まで指定できます。~~

- ~~16 進数間にアンダーバー“\_”を任意に入れることができます。~~

- ~~設定数値 x 20nsec がディレイ時間となります。~~

- ~~デフォルトは 0000\_1000 が設定され、約 82usec のディレイ間隔が得られます。~~

(k) #P : D1 = xxxx\_xxxx

- nSTATUS がリリースされて、送信の許可をモジュールに出すまでのディレイ間隔を指定します。

- 指定は 16 進数で行い、8 衔全てを指定する必要があります。

- 0000\_0000 から FFFF\_FFFF まで指定できます。

- 16 進数間にアンダーバー“\_”を任意に入れることができます。

- 設定数値 x 20nsec がディレイ時間となります。

- Pump\_On コマンド( #P:C1 コマンド) が OFF のときの緩やかな立ち上がりを考慮して、デフォルト値として 0000\_0010 が設定されており、20nsec x 16=320nsec 後に DCLK がアクティブになります。

- ワードアライナ機能が有効な場合(#P:C0=1)、有意なデータまで読み飛ばすため、データが出力されるまでにさらに時間を要する場合があります。

- アルテラ FPGA では、RBF ファイルの使用を推奨しているため、ワードアライナを設定する必要がありません。

(l) #P : D2 = xxxx\_xxxx

- XRST が High になって nCONFIG を High にするまでの間隔を指定します。

- 指定は 16 進数で行い、8 衔全てを指定する必要があります。

- 0000\_0000 から FFFF\_FFFF まで指定できます。

- 16 進数間にアンダーバー“\_”を任意に入れることができます。

- 設定数値 x 20nsec がディレイ時間となります。

- SD カードからのコンフィギュレーションの場合、SD カード読み出し準備時間の 17msec より短い時間設定した場合、機能しません。

- デフォルトは 000D\_0000 が設定され、約 15.7msec の遅延が挿入され、SD カード読み出し準備時間による遅延による動作と、ほぼ等価となります。

(m) #P : C0/1/2/3/4/5/6/7/8/9 = 0/1

- 0 から 9 のコントロールビットが定義されています。

① #P : C0 = 0/1 ワードアライナ機能

- 本パラメータはアルテラ FPGA では使用しません。デフォルトのままとして下さい。

- 本パラメータに“1”を設定すると、バイナリデータの先頭付近に存在する文字情報を読み飛ばし、文字情報のあとに位置する 32 個の FF によるプリアンブル領域が先頭となるようにワードアライナを行います。(9.1 ワードアライナ機能 参照)

- 先頭の文字情報がなく、32 個の FF によるプリアンブルから始まるデータは、FF の数を損なうことなく出力されます。

- 本パラメータを設定した状態で、32 個の FF(検出は 5 個の FF で実行しています。)が存在しない場合、データは出力されないことになります。

- pof ファイルに適用すると、先頭領域の管理情報が削除され、rbf ファイルとほぼ同じフォーマットになります。

- 本機能は、FPGA のデータバスが 16bit,32bit の時には位相補正機能としても働き、Xilinx のように、バス幅を識別させるための識別パターンが存在する場合、先頭に存在する文字情報の長さに関わらず、32bit 単位でしっかりと調整することが可能となります。

② #P : C1 = 0/1 nCONFIG、Pump ON 指定

- 本パラメータに“1”を設定すると、nCONFIG 信号を、Low からリリースするときに、50MHz 1clk 分(20nsec)High レベルを出力し、その後 High-Z を出力し、信号の立ち上がりを鋭角にすることが可能です。

デフォルト (“0”)

## ③ #P : C2 = 0/1

- 本パラメータに“1”を設定すると、FPP モードにおいて、8bit のデータバスを 4 つの区画に分け、それぞれの区画の 2 ビット単位でパラレルシリアル変換して出力されます。

D[1:0] =&gt; D[0]

D[3:2] =&gt; D[2]

D[5:4] =&gt; D[4]

D[7:6] =&gt; D[6]

- ビットの出現順番は、#P : SS コマンドに準拠します。（“1”の時 LSB first）

- #P:C2 と #P:C3 コマンドは、C3 コマンドが優先されます。

- 本モードを使用するためには、バイナリデータを事前に多重しておく必要があります。

## ④ #P : C3 = 0/1

- 本パラメータに“1”を設定すると、FPP モードにおいて、8bit のデータバスを 2 つの区画に分け、それぞれの区画の 4 ビット単位でパラレルシリアル変換して出力されます。

D[3:0] =&gt; D[0]

D[7:4] =&gt; D[4]

- ビットの出現順番は、#P : SS コマンドに準拠します。（“1”の時 LSB first）

- #P:C2 と #P:C3 コマンドは、C3 コマンドが優先されます。

- 本モードを使用するためには、バイナリデータを事前に多重しておく必要があります。

## ⑤ #P : C4 = 0/1

- 本パラメータに”1”を設定すると、Done 信号を無視します。

- DONE 信号を uSDCONF1A に接続しない回路構成系において、DONE 信号端子をオーブンのままにしておくと、内部 PullUp によって常に High と見えるため、コンフィギュレーションが完了したと判断し、Data バスを High-Z にして、ユーザーに開放します。

- 本設定は、DONE 信号を無視し、FPGA にデータを出し続けるためのパラメータです。

## ⑥ #P : C5 = 0/1

- FPP で AES や DeComp 機能を有効にすると、1 つの 8 ビットデータに対して 4 回 DCLK 入力してあげる必要があります。

- 本パラメータに”1”を設定することで x4 モードをサポートします。

- MSEL も FPP x4 の設定を選択して下さい。

- 本パラメータを設定した状態で、XMODE ピンを PS モードに設定すると、DCLK は x1 モード動作に自動遷移します。（PS モードでは、AES や Decom は x1 モードで動作します。） FPPx4 と PS モードが選択できるシステムでは、常に”1”に設定してあれば、モジュールが自動で切り替えてくれます。

- ~~尚、PS モードで AES や Comp 機能を有効にする場合、DCLK は x1 で動作するため、本パラメータは”0”に設定する必要があります。（2013.07.02）~~

D[7:0] DCLK

図 8.3 FPPx4 の出力波形

## ⑦ #P : C6 = 0/1

- 0:+コマンドによる連結時の出力。

1:copy コマンドによる連結時の出力。

- 複数バイナリファイルをコンフィギュレーションする場合の XCSI の出力方法の選択を行ないます。

- DOS プロンプト上で以下のコマンドで連結したバイナリファイルを使用する場合、本パラメータは”1”に設定する必要があります。

- > copy file1.bin/B+ff4096.bin/B + file2.bin/B (+ ff4096.bin/B + file3.bin/B) mergfile.bin

/B はバイナリファイルを意味します。

ff4096.bin は 4096 バイトの ffh が書き込まれたファイルです。(添付ファイル)

()内を繰り返すことにより、最大 8 個のバイナリファイルを連結することができます。

mergfile.bin は連結後のファイル名になります。

バッチファイルで予め準備しておくと、生成を単純化することができます。

- +コマンドによる連結の場合、本パラメータは”0”に設定する必要があります。

- ALTERA FPGA で使用することはありません。

## ⑧ #P : C7 = 0/1

- ”1”にセットすると、XCS0,XCS1 の 2 本の制御信号により、外付け回路を制御し、7 本の XCS[6:0]信号を生成し、最大 7 個の FPGA に対してマルチにコンフィギュレーションを行うことが可能となります。

- デフォルト(0)

## ⑨ #P : C8 = 0/1

- 未定義 (Reserved)

## ⑩ #P : C9 = 0/1

- 本コマンドを ON にすると、動作モードに関わらず、モジュールのバージョン情報が LED の点滅により表示されます。

- 表示は 16 ビット単位で一巡し、長い点灯は”1”を、短い点灯は”0”を意味します。

- 先頭から 4bit 単位で区切って Hex 変換すると、モジュールのバージョン情報が得られます。

- 先頭の 4bit がバージョンを、次の 4bit とその次の 4bit の 2 衔でリビジョンを、最後の 4bit でサフィックスを表します。

- バージョン情報は、大きな変更があった場合に変更されます。

- リビジョンは、簡易な変更があった場合に変更されます。

- サフィックスは、同一バージョン、サフィックスにおいて、出力電圧などに違いを持たせた場合に割り付けられます。

- 表示方法の詳細は 8.3. バージョン情報表示機能の項目をご参照下さい。

## (n) #R : 0～F

- ・ コンフィギュレーション失敗時のリトライ回数を指定します。

- ・ 0 回から 15 回まで指定できます。(デフォルト 0)

- ・ ポストアンブルを送信し終わった段階で DONE 信号をモニタし、アクティブになっていない場合コンフィギュレーションが失敗したと判断し、nCONFIG を Low に落としてコンフィギュレーションをやり直します。

- ・ nSTATUS によるコンフィギュレーションの失敗の監視は行っていません。

## (o) bitfile-name

- ・ 上記の(a)または(b)に属さないキャラクタで始まる行は、Line-Processor はバイナリデータ名として扱います。(注: Line-Processor はキャラクタを解析するシケンサ論理)

- ・ バイナリデータは、“.rbf”フォーマットを指定して下さい。

- ・ バイナリデータ名は 8 文字以下である必要があります。(拡張 FAT16 未対応)

- ・ バイナリデータ名の前後にスペースや TAB を含むことができます。(ファイル名の間にスペースや TAB を挿入することはできません。)

- ・ バイナリデータ名を”+”で連結することにより 8 個の FPGA まで CS 制御による Multi-FPGA コンフィギュレーションを行うことが可能です。 bitfile1.rbf + bitfile2.rbf + bitfile3.rbf + bitfile4.rbf

- ・ “+”による連結の際、バイナリデータ名と”+”の間には必ず 1 つ以上の空白を挿入して下さい。

- ・ “+”による連結の際、途中に改行を加えないで下さい。

## (p) #0～#F : bitfile name

- ・ バイナリデータ名を 0 から F の 16 個の 16 進数と関連付けを行います。

- ・ 本コマンドにより関連付けが行われた場合、AREA ロータリー-SW の指定エリアと同一の番号の関連付けが存在した場合、関連付けされたバイナリデータをコンフィギュレーションの対象とします。

- ・ # の後には、0～9(30h～39h), A～F(41h～46h) 若しくは a～f(61h～66h)を置くことができます。

- ・ “:” の後に関連付けをしたいビットファイル名を記述します。

- ・ バイナリデータは、“.rbf”フォーマットを指定して下さい。

- ・ バイナリデータ名は 8 文字以下である必要があります。(拡張 FAT16 未対応)

- ・ バイナリデータ名の前後にスペースや TAB を含むことができます。(ファイル名の間にスペースや TAB を挿入することはできません。)

- ・ バイナリデータ名を”+”で連結することにより外付け無しで 2 個の FPGA まで CS 制御による Multi-FPGA コンフィギュレーションを行うことが可能です。

#0:bitfile1.rbf + bitfile2.rbf

- ・ 外付け回路を追加することにより、最大 7 個までの FPGA のコンフィギュレーションを行うことが可能です。

- ・ “+”による連結の際、バイナリデータ名と”+”の間には必ず 1 つ以上の空白を挿入して下さい。

- ・ “+”による連結の際、途中に改行を加えないで下さい。

#### 8.4. D1,D2,PO の設定について

- D2 パラメータは、ALTERA のパラメータの tCFG(nCONFIG low pluse width)に該当し、2usec 以上です。uSDCONF1A では SDCard から config.txt とバイナリファイルの先頭を読み出し終わるまでの間、約 17msec 間 Low にして、動作可能になるのを待ちます。NandFlash からの読み出し時もこれに合わせるため、D2=000C\_0000(=15.7msec)をデフォルトとしています。(uSDCONF1A には NandFlash は搭載されていませんが、Nand 搭載版と共に論理を使用しているため、共通のデフォルト値が採用されています。)

- D1 パラメータは、ALTERA のパラメータの tST2CK(nSTATUS high to first rising edge of DCLK)に該当します。

- 推奨地として D1=0000\_0200(=10uSec)。config.txt でなにも指定しない場合、D1=0000\_2000(=164usec)になります。

- PO パラメータは、ALTERA パラメータの USRCLK 数とみなしてそれより大きい数値を設定して下さい。

- 表 8.1 は、代表的な FPGA のシリーズのこれらのパラメータを列記した表です。

- FPGA のシリーズにより、これらの値は異なり、共通に使える値はありません。このため、これらのパラメータを理解し、条件に合致した値を選択する必要があります。

- 一覧にない FPGA をコンフィギュレーションする場合は、これらの値を調査し、最適な値を設定して下さい。

図 8.3

| FPGA Series | tCF2ST1                 | tCF2CK                  | tST2CK              | CLKUSR              | D1                 | D2                   | PO                     |

|-------------|-------------------------|-------------------------|---------------------|---------------------|--------------------|----------------------|------------------------|

| Cyclone-III | $\leq 800\mu\text{s}$   | $\geq 800\mu\text{s}$   | $\geq 2\mu\text{s}$ | 3,185/<br>3,192(LS) | 0000_0200<br>=10uS | 000C_0000<br>=15.7mS | 0000_1000<br>=4096clk  |

| Cyclone-IV  | $\leq 230\mu\text{s}$   | $\geq 230\mu\text{s}$   | $\geq 2\mu\text{s}$ | 3,192               | 0000_0200<br>=10uS | 000C_0000<br>=15.7mS | 0000_1000<br>=4096clk  |

| Cyclone-V   | $\leq 1,506\mu\text{s}$ | $\geq 1,506\mu\text{s}$ | $\geq 2\mu\text{s}$ | 17,408              | 0000_0200<br>=10uS | 000C_0000<br>=15.7mS | 0000_5000<br>=20480clk |

| Stratix-III | $\leq 100\mu\text{s}$   | $\geq 100\mu\text{s}$   | $\geq 2\mu\text{s}$ | 4,436               | 0000_0200<br>=10uS | 000C_0000<br>=15.7mS | 0000_1200<br>=4608clk  |

| Stratix-IV  | $\leq 500\mu\text{s}$   | $\geq 500\mu\text{s}$   | $\geq 2\mu\text{s}$ | 8,532               | 0000_0200<br>=10uS | 000C_0000<br>=15.7mS | 0000_2400<br>=9216clk  |

| Stratix-V   | $\leq 1,506\mu\text{s}$ | $\geq 1,506\mu\text{s}$ | $\geq 2\mu\text{s}$ | 17,408              | 0000_0200<br>=10uS | 000C_0000<br>=15.7mS | 0000_5000<br>=20480clk |

| Arria-GX    | $\leq 100\mu\text{s}$   | $\geq 100\mu\text{s}$   | $\geq 2\mu\text{s}$ | 299                 | 0000_0200<br>=10uS | 000C_0000<br>=15.7mS | 0000_0200<br>=512clk   |

| Arria-II    | $\leq 500\mu\text{s}$   | $\geq 500\mu\text{s}$   | $\geq 2\mu\text{s}$ | 8,532               | 0000_0200<br>=10uS | 000C_0000<br>=15.7mS | 0000_2400<br>=9216clk  |

| Arria-V     | $\leq 1,506\mu\text{s}$ | $\geq 1,506\mu\text{s}$ | $\geq 2\mu\text{s}$ | 17,408              | 0000_0200<br>=10uS | 000C_0000<br>=15.7mS | 0000_5000<br>=20480clk |

表 8.1 D1,D2,PO 設定例

## 8.5. コマンドパラメータ デフォルト値

- “CONFIG.TXT”設定されるパラメータのデフォルト値を示します。

| Maker Code | Maker Name | デフォルト設定値                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 備考 |

|------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 指定無        | —          | #P : SS = 0 (MSB ファースト)<br>#P : SB = 1 (Swap 無し)<br>#P : SW = 0 (Swap 無し)<br>#S : 0 (50MHz Passive モード)<br>#P : PR = 0000_0100 (プリアンブルなし)<br>#P : PO = 0001_0000 (ポストアンブル 65536CLK 挿入)<br>#P : PM = 0000_1000 (ミドルアンブル 4096CLK 挿入)<br>#P : D0 = 0000_1000 (nCONFIG ~ nSTATUS : 82usec)<br>#P : D1 = 0000_0010 (nSTATUS ~ DCLK : 320nsec)<br>#P : D2 = 000C_0000 (XRST~nCONFIG : 15.7msec)<br>#P : C0 = 1 (ワードアライナ有効)<br>#P : C1 = 0 (Pump ON 無効)<br>#P : C2 ,C3= 0 (Bus 分割 Multi FPGA mode 無効)<br>#P : C9 = 0 (バージョン表示モード 無効) |    |

| A          | Altera     | #P : SS = 1 (MSB ファースト)<br>#P : SB = 0 (Swap 無し)<br>#P : SW = 0 (Swap 無し)<br>#S : 0 (50MHz Passive モード)<br>#P : PR = 0000_0000 (プリアンブルなし)<br>#P : PO = 0000_4000 (ポストアンブル 4096CLK 挿入)<br>#P : D0 = 0000_1000 (nCONFIG ~ nSTATUS : 82usec)<br>#P : D1 = 0000_2000 (nSTATUS ~ DCLK : 164usec)<br>#P : D2 = 000C_0000 (XRST~nCONFIG : 15.7msec)<br>#P : C0 = 0 (ワードアライナ無効)<br>#P : C1 = 0 (Pump ON 無効)<br>#P : C2 ,C3= 0 (Bus 分割 Multi FPGA mode 無効)<br>#P : C9 = 0 (バージョン表示モード 無効)                                              |    |

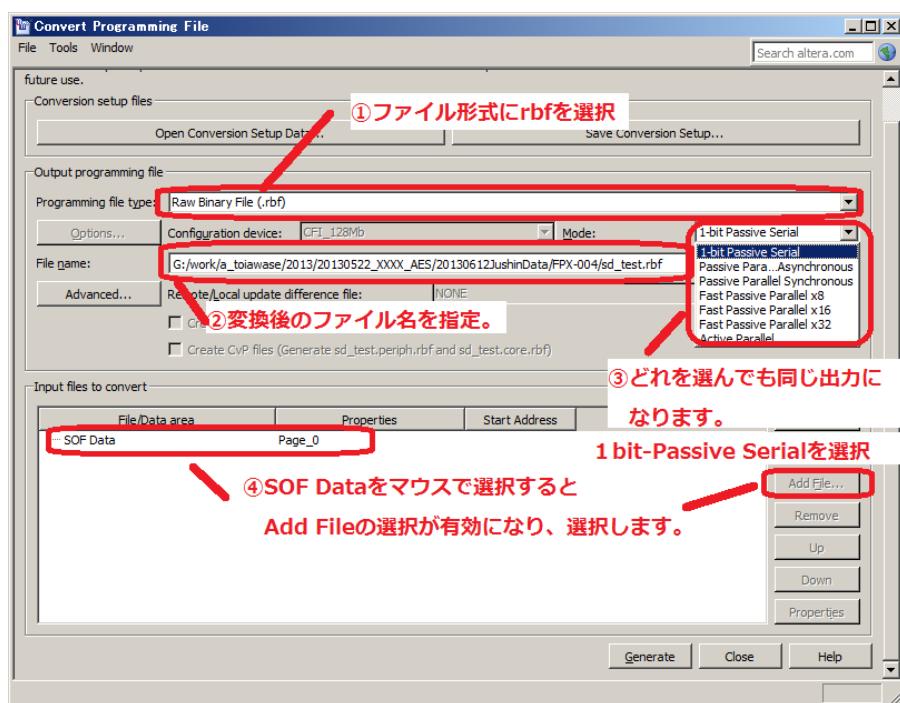

## 8.6. RBF データの生成方法

Quartus-II の左上の PullDown メニューから、

File > Converter Program Files を選択します。

下記の Window が現れます。

ファイル形式に rbf を選択します。

変換後のファイル名を指定します。8 文字以内で指定すると、そのまま SDCard にコピーが可能です。

モードを指定します。どれを選択しても rbf は同じ出力を吐き出しますので

とりあえず、1-bit Passive Serial を選択します。

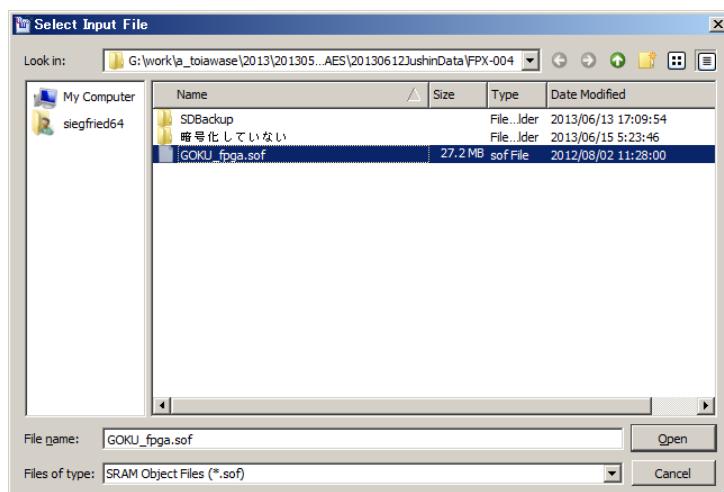

ファイル名を選択し、Open をクリックします。

Generate をクリックすると rbf ファイルが出力されます。

生成された rbf を SDCard のルートディレクトリにコピーします。

## 9. 機能詳細

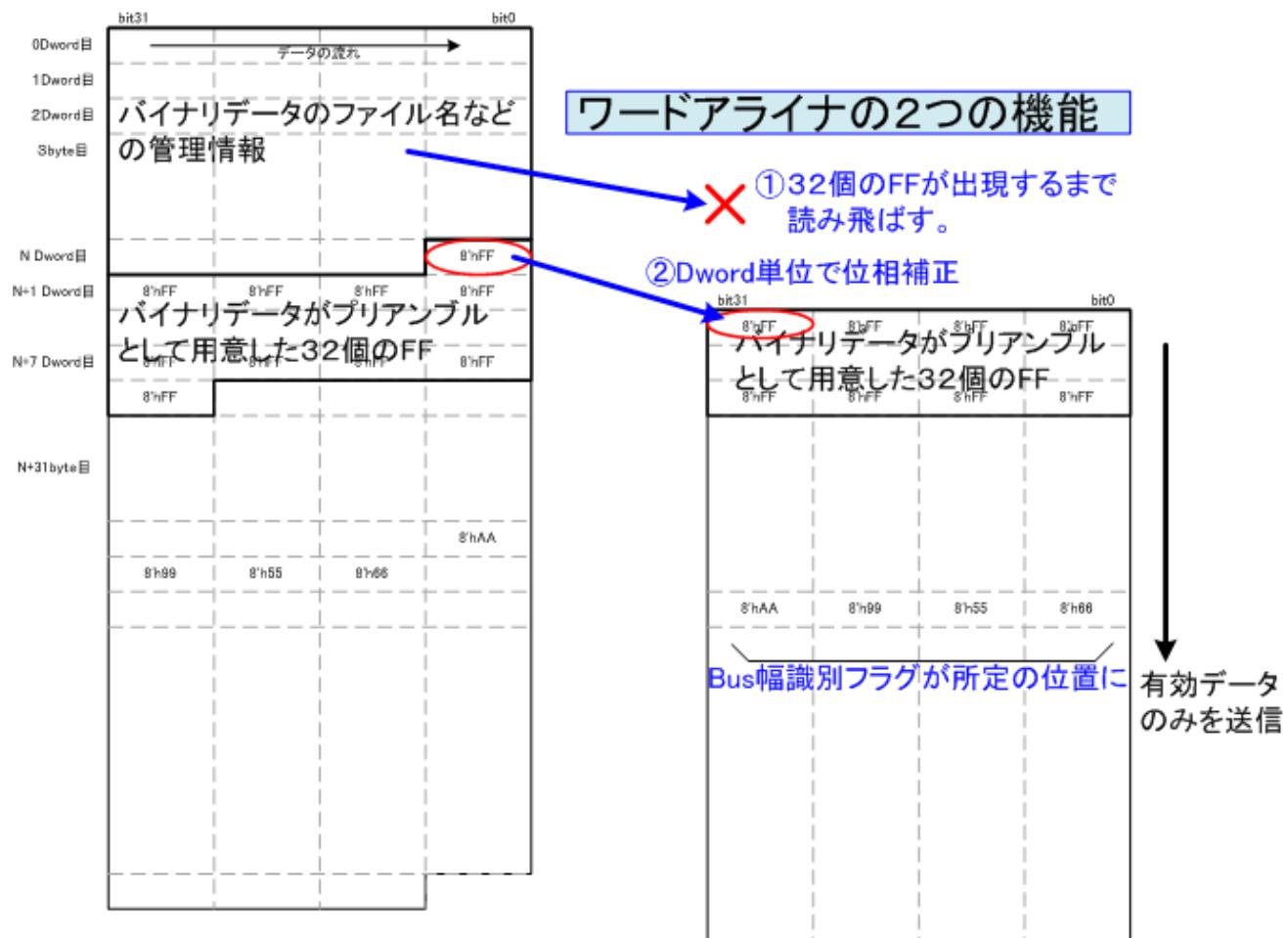

### 9.1. ワードアライナ機能

- バイナリデータ上の実質的な送信開始情報である 32 個の FF を検出します。

- FPGA に転送不要な管理情報等を削除します。

- 16bit や 32bit 幅で FPGA に転送するとき、有効データの始まりのバイト位置をダブルワード単位で位相を補正して FPGA に転送します。

- 本機能により、配置配線の結果として出力されるサフィックスが“pof”的バイナリデータや、サフィックスが“bit”的バイナリデータを取り扱うことが可能になります。

- “CONFIG.TXT”的 #P : C0 コマンドで“1”を指定することにより有効になります。

(デフォルト 0)(メーカ指定した場合はデフォルト1)

- 現状、ALTERA FPGA に対しては、RBF ファイルを使用することを推薦しています。RBF ファイルの先頭には管理ファイルが存在しないため、本設定は常に“0”にして下さい。

図 9.1. ワードアライナ機能説明図

## 9.2. bit 連結による Multi FPGA Configuration 機能

- 添付されるアプリケーションソフトと、コマンドパラメータの設定により、シリアル転送により同時に複数の FPGA をコンフィギュレーションすることができます。

- Daisy-Chain 方式による複数の FPGA をコンフィギュレーションする方法とは別的方式になります。

- microSD カードの実効読出速度が 200Mbps に対して、50Mbps のシリアル通信を 1 本だけ行うことには非効率で、本方式によりリソースを分割することにより、4 本まではシリアル通信の実効速度を下げる事なく転送することが可能になります。

- 分割個数が 8 個の場合で、FPGA 割り当てに空きがある場合や、それぞれの FPGA のサイズが異なる場合、Daisy-Chain 方式より効率が悪くなる場合があります。

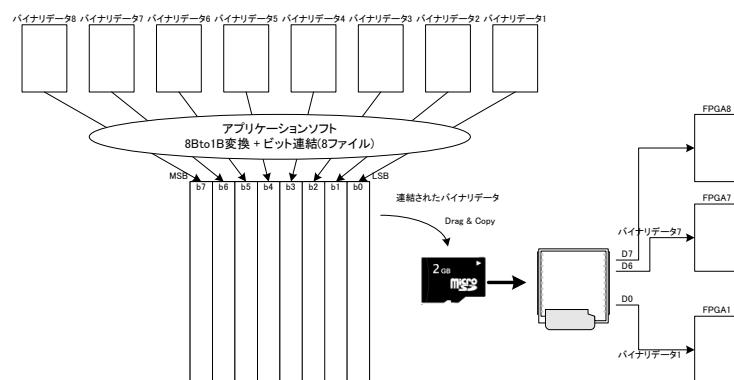

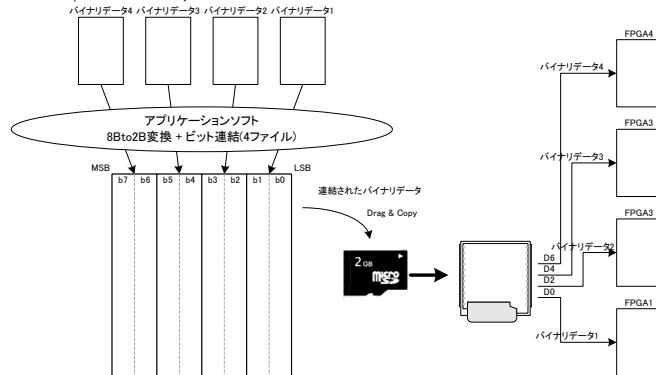

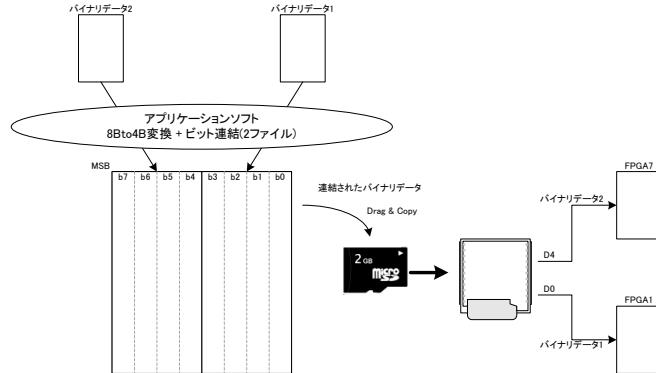

bit連結によるMulti FPGA Configurationの動作原理

(1)8分割時(#P : C2 = 0, #P : C3 = 0)

(2)4分割時(#P : C2 = 1, #P : C3 = 0)

(3)2分割時(#P : C2 = 0, #P : C3 = 1)

図 9.2. bit 連結による Multi FPGA Configuration の動作原理図

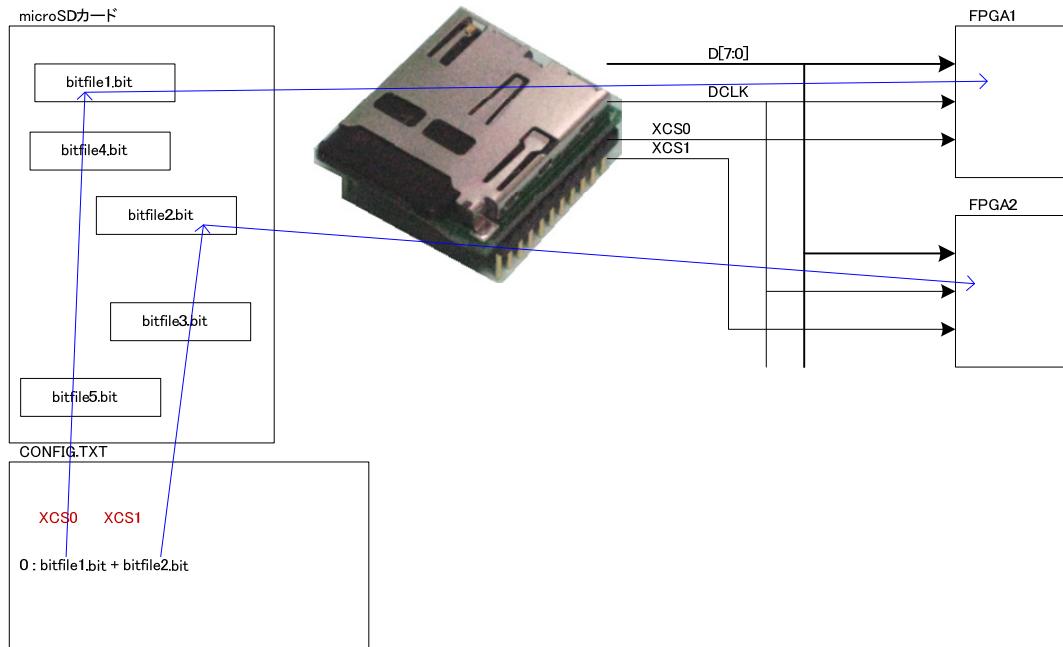

### 9.3. “CONFIG.TXT”による Multi FPGA Configuration 機能

- “CONFIG.TXT”ファイル上で単独バイナリデータを指定する代わりにバイナリデータを順次”+”により連結指定することにより、モジュールは最初のバイナリデータの転送を CS0 をアサートして開始し、転送が終了するとネゲートし、順次 CS 番号をインクリメントしながら該当のバイナリデータを転送することが可能です。

図 9.3 “CONFIG.TXT”による Multi FPGA Configuration の動作原理図

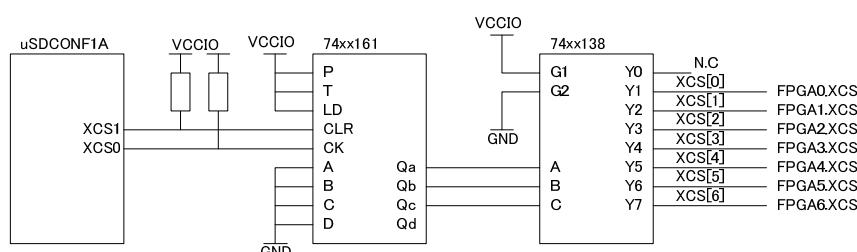

### 9.4. 外付け回路による最大 7 個の Multi FPGA Configuration 機能

- 下記外部回路を実装し、かつ、“CONFIG.TXT”ファイル上で#p:C7=1 を設定すると、外部で生成した XCS[6:0]信号により、最大7個の FPGA をマルチにコンフィギュレーションすることが可能になります。

- 74xx161 の Qd を使用して、74xx138 を追加することで、最大8個の FPGA をマルチにコンフィギュレーションすることが可能になります。

図 9.4

## 10. uSDCONF1A と uSDCONF1F の共存について

### 10.1. uSDCONF1F 用の基板に uSDCONF1A を実装する場合

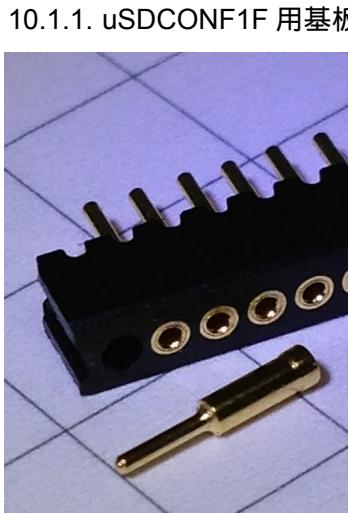

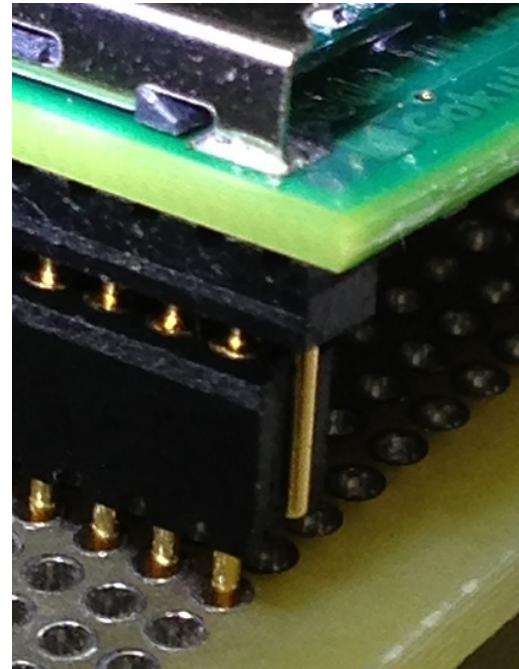

図 10.1

図 10.2

図 10.3

- 図 10.1 は、添付される MAC8 の OQ-11-5-12P ソケットから 1pin を取り外した写真です。

取り外しは、ラジオペンチの先で pin 先を挿入方向に沿って押すと簡単に外せます。

- 取り外した OQ-11-5-12P ソケットを、取り外した側を前面にして実装します。(図 10-2)

- ソケットに uSDCONF1A を実装すると、前面側の手前の pin(図 10.2 の写真では PIN24)が、図 10.1 でピンを抜いたモールドの穴部分に隠れ、静電気や外圧から守られます。

- ソケット前面端は、OQ-11-5-11P ソケットを実装した場合より、前面に約 1.27mm ほどモールド部分が飛び出します。

- 図 10.3 は、uSDCONF1F を実装した写真です。uSDCONF1A の 24pin が存在する箇所に LED が存在しますが、コネクタ間との距離も十分保たれています。

- OQ-11-5-12P ソケットは、uSDCONF1A 前面先端内に位置していますが、OQ-11-5-11P ソケット実装時の前面先端から 1.27mm 以内に部品が配置されている場合は、モールド部分に部品が干渉して本方式を適用できないかもしれません。その場合は、モールド部分の干渉部分をカットするか、uSDCONF1A の 1pin、24pin をカットする必要があります。

- ご購入検討時にご相談下さい。

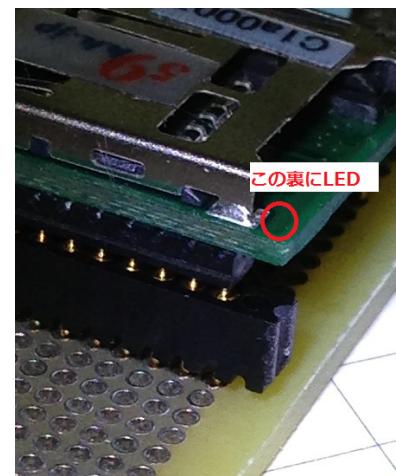

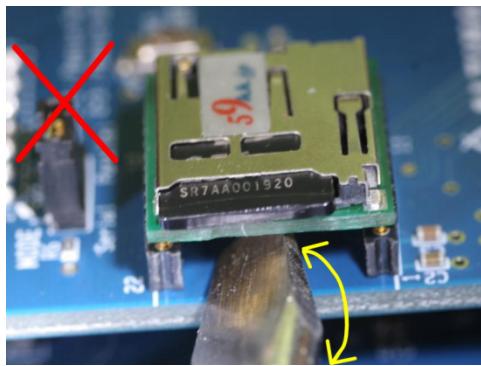

## 10.1.2. uSDCONF1F 用ソケットが既に実装されている場合

図 10.4

図 10.5

- 図 10.4 のように、ソケットの両端は、下側のようにピンを取り外してカットされて曲面を持った側と、上側のように、ベースとなるソケットの終端部分で曲面のない先端をもつタイプがあります。

- 図 10.4 の下側の場合、図 10.5 のようにモールドの内側に湾曲した部分にピンが潜り込みますが、図 10.4 の上側の先端が前面にきている場合、ピンが外側に押し出されて曲がってしまいます。

- この場合、下記より方法を選択して下さい。

ソケットを取り外し、12pin 用に付け直す。

モールド部分の接触部分をルーター等で削り、接触しないようにする。

uSDCONF1A の前面外側のピンをカットする。

- 上記処理は、悟空株式会社で行うことが可能ですが。(有償となります。)

- また、カットしたピンの付け直しも行います。(有償となります。)

## 11. モジュールのソケットからの取り外しについて

- uSDCONF1A はモジュール構成となっているため、ターゲット基板に実装する際にソケット実装することで、システムの評価が終了したあとに取り外して他のシステムに使いまわすことが可能です。

- しかしながら、図 11.1. のように、モジュールの裏側は高密度にチップ部品を実装しており、取扱いに注意して取り外さないと不用意に部品を押しつぶしたり、パターンを剥離してしまいかねません。

- 本章では、モジュールを末永くお使いいただくために、モジュールの裏面の実装の状況を把握していただき、取り外しの注意点等を紹介いたします。

### 11.1. モジュール裏面

- “59kk”のシールの下に制御用のチップが実装されています。

その両側の赤枠で囲った部分には、チップ抵抗やチップコンデンサ、ロジックチップが密集して実装されています。

図 11.1. uSDCONF1A Bottom View

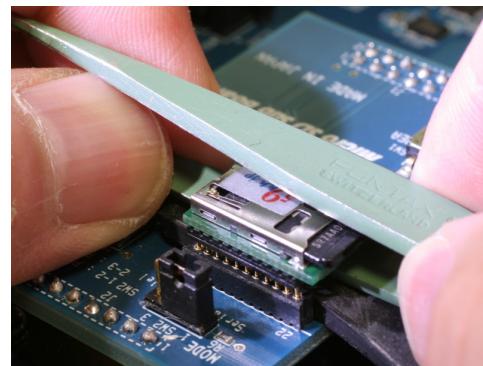

### 11.2. モジュールの取り外し方

- ドライバ等でモジュールをソケットから抜き取る場合、図 11.1 の部品配置を常にイメージして、赤枠部分に力がかかるないよう十分に注意して下さい。

- “59kk”のシールの貼られた制御チップの高さは 1.3mm あり、他の部品より背高です。

ドライバ等で引き抜かれる場合は、こちらのチップに垂直に持ち上げる方向に力がかかるように、ゆっくりと、そして四隅が均等に持ち上がるよう少しづつ操作を繰り返して下さい。

- 一気に持ち上げると、四隅のうちの一か所だけが持ち上がってしまってピンが曲がる原因になります。

- ドライバ等で取り外す場合、図 11.2 のようにモジュール下への差し込みが十分でない場合、図 11.1 の赤枠の部分に作用点が働いてしまうとチップ部品を破損してしまいます。

また、下の基板に部品が配置されている場合、下の基板の部品を破損してしまう恐れがあります。

- 図 11.3 のように、ピンセットをモジュールの下を通して、両側から少しづつ持ち上げるとスムーズに取り外せます。

図 11.2 取り外しの悪い例

図 11.3 ピンセットを使った例

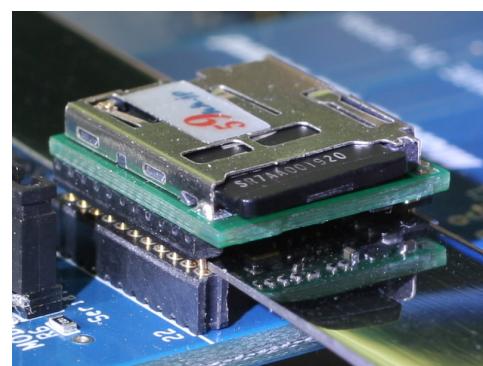

- 図 11.4 は D.I.Y で使用する“目地用コーリングヘラ”です。

- 図 11.5 はヘラをモジュール下に滑り込ませた写真です。

ソケットの台座部分に滑り込んでいるのが判ります。

この状態で両側から両手で少しづつ持ち上げると部品に接触することなく取り外しが可能です。

- こちらのヘラは、Amazon やコーナン PRO などでお買い求めいただけます。

下記品名で検索をかけると Amazon やコーナン PRO が上位にヒットします。

尚、モジュールご注文の際に弊社で調達することも可能です。ご入り用の際は弊社までお問い合わせください。

- 品名：目地用コーリングヘラ曲り

発売元：株式会社ハンディ・クラウン

商品コード：309018 0000

注文型番：4905533-152782

図 11.4 目地用コーリングヘラ

図 11.5 ヘラ使用例

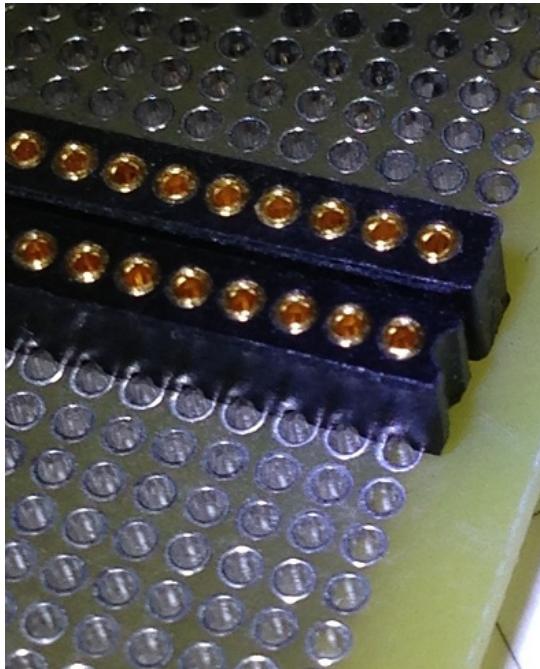

## 12. 添付品

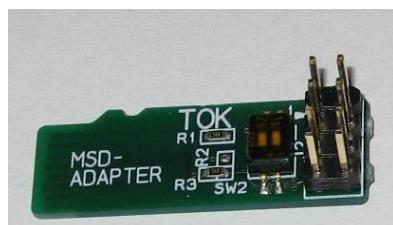

図 12.1

図 12.2

- 図 12.1 は製品として出荷される構成要素です。

- uSDCONF1A 本体

- 2 Gbyte microSDCard ( メーカはそのときの入手状況によって異なる場合があります。 )

SDCard の中の readme ディレクトリ内に、下記のデータが書き込まれています。

- (ア) Datasheet

- (イ) CONFIG.TXT サンプル(ALTERA、Xilinx 用)

- SDCard アダプタ

- MAC-8 ME-10-10-12P 若しくは ME-1-10-12P ソケット 2個

- 静電マット

- 乾燥剤 + 静電袋 + ブリスタークース

- 図 12.2 はケースに梱包された状態です。

- ケースのサイズは、突端部分を含めて 50mm × 85mm × 20mm です。

- 数量が多く、即実装される場合には、梱包しないで出荷も可能です。

### 13. VCCIO 電圧とシールの色

- uSDCONF1A の VCCIO 電圧を識別できるよう、microSD ソケット表面に丸いシールが張られています。(表 13.1 参照)

- 3.3V と 2.5V のモジュール内部の設定が共通のため、3.3V/2.5V を青色シール 1 枚で代用する場合があります。

| VCCIO | インターフェース  | シール |

|-------|-----------|-----|

| 3.3V  | LVCMS3.3V | 青色  |

| 2.5V  | LVCMS2.5V | 緑色  |

| 1.8V  | LVCMS1.8V | 黄色  |

表 13.1

図 13.1 シール添付例

### 14. 発注型格

- 発注時、下記の型格でご注文下さい。

- 数量が多い場合などで、即実装される場合は、静電マット平面梱包が便利です。

| VCCIO 電圧  | 梱包形態         | 発注型格                |

|-----------|--------------|---------------------|

| 3.3V/2.5V | プリスタークース単体梱包 | uSDCONF1A5-001-33V  |

|           | 静電マット平面梱包    | uSDCONF1A5-001-33VN |

| 1.8V      | プリスタークース単体梱包 | uSDCONF1A5-001-18V  |

|           | 静電マット平面梱包    | uSDCONF1A5-001-18VN |

表 14.1 発注型格表

## 15. 制約事項

- ① SD カードは、添付の2G バイト品をご使用下さい。

市販の2G バイト以下の FAT16 でフォーマットされた SD カードもご利用いただけますが、初期のころの SD カードインターフェース速度が極端に遅いものや、最近のものでも、極まれに相性が合わない場合があります。

この場合、SD カードからのコンフィギュレーション時、転写時に LED が点灯したままの状態になります。

FAT32 でフォーマットされている 2G バイトを超える SDHC 品には対応していません。

2G バイト以下の microSD カードでも、FAT32 で再フォーマットされたものは動作しません。

再フォーマットを行う場合は FAT16(Microsoft Windows のボリュームのプロパティのファイルシステムでは FAT と表示されます )を選択して下さい。

- ② ビットファイル名は英数字の 8 文字以下にして下さい。

拡張 FAT16 には対応していません。

大文字小文字どちらも使用できますが、識別は行いません。

“\_”(アンダーバー)、“-”(ハイフン) も文字として使用できます。

尚、8 文字以上のファイルを一旦 microSD カードにコピーして、rename によりファイル名を 8 文字以下に修正させた場合、修正後も依然 8 文字以上のファイルとして取り扱われてしまい、先頭の 7 文字しかファイル名の識別要素として機能致しませんので、パソコンでファイル名を修正後、コピーを行って下さい。

- ③ “CONFIG.TXT”ファイルやバイナリデータの microSD カードへのコピーは、Windows システムより行って下さい。

Linux や Unix システム上で microSD カードにコピーすると、正しく動作しません。

(Linux や Unix 上で生成されたバイナリデータを、Windows システムを介してコピーする分には問題ありません。)

- ④ bit 連結による Multi FPGA Configuration 機能はインプリメントされていますが、バイナリデータを連結するためのアプリケーションソフトを準備中です。

- ⑤ DCLK のクロック速度選択機能で、DCLK を受信して動作するアクティブモードは定義されていますが、現在インプリメント作業中です。

## 16. アップデート機能(順次対応予定)

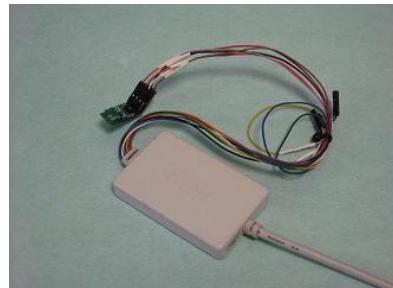

“59kk”のシールの貼られたモジュールは、128 ビットの暗号 Key によって Encryption がかけられています。msd-Adapter と JTag ケーブルをご用意いただくことにより、同じ暗号 Key によって暗号化された bit ファイルを悟空株式会社のホームページよりダウンロードしてアップデートしていただくことが可能です。

“59kk”のシールの貼られていないモジュールにつきましては、暗号 Key の書き込みが必要ですので、弊社もしくは担当営業にご相談下さい。

(JTag ケーブルは、悟空株式会社にても販売する予定です。)

今後、下記のようなアップデートを予定しています。

- 機能改版 (一部有償)

- ✧ FAT32 対応

- ✧ SDHC 対応

- ✧ コンフィギュレーション終了後の microSD カードへのインターフェース機能

- ✧ SPI(Master/Slave)終端機能

- ✧ JTag 終端機能

- JTag からのコンフィギュレーション

- ROM データの書き換え

- 別の uSDCONF の書き換え

- など

以上

### お問い合わせ等連絡先

悟空株式会社

担当：大庭（オオバ）

〒 222-0033

横浜市港北区新横浜 1-19-3 アドホックビル 4F-E

FreeCall : 0800-7775559 ( 平日 9:00~18:00 )

電話 : 045-590-6227 Fax : 050-3156-1404

Email : [info01@59kk.jp](mailto:info01@59kk.jp) URL : <https://www.59kk.jp>